-

; ) 关于网口晶振25MHz/50MHz辐射超标问题的建议

(晶振辐射超标) 网口EMC辐射超标是硬件设计中非常经典的难题。它的根源往往是一个“干扰源”加上一条“发射天线”的组合——板上的高频噪声(比如晶振的谐波)通过网口这个路径,以共模电流的形式耦合到网线上,而网线本身就是一根高效的 antenna,将噪声辐射出去。 简单来说,网口晶振(如:25MHz/5…时间:2025/11/13

关于网口晶振25MHz/50MHz辐射超标问题的建议

(晶振辐射超标) 网口EMC辐射超标是硬件设计中非常经典的难题。它的根源往往是一个“干扰源”加上一条“发射天线”的组合——板上的高频噪声(比如晶振的谐波)通过网口这个路径,以共模电流的形式耦合到网线上,而网线本身就是一根高效的 antenna,将噪声辐射出去。 简单来说,网口晶振(如:25MHz/5…时间:2025/11/13 -

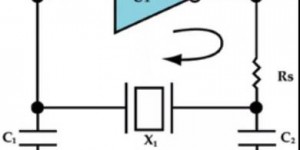

; ) 无源晶振串联0欧姆电阻串联在哪里?

(无源晶振电路中0欧姆串联电阻位置:Rext处) 无源晶振串联0欧姆电阻串联在哪里? 答:0欧姆串联电阻通常位于晶振与微控制器时钟信号输出脚之间。 串联0欧姆电阻具体位置如下: 晶振频率管脚:电阻的一端连接晶振的其中一个频率引脚。 芯片时钟信号输出脚:电阻的另一端连接微控制器的时钟输出引脚(OSC_…时间:2025/04/06

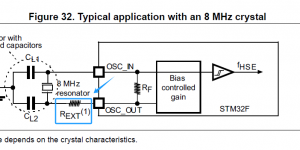

无源晶振串联0欧姆电阻串联在哪里?

(无源晶振电路中0欧姆串联电阻位置:Rext处) 无源晶振串联0欧姆电阻串联在哪里? 答:0欧姆串联电阻通常位于晶振与微控制器时钟信号输出脚之间。 串联0欧姆电阻具体位置如下: 晶振频率管脚:电阻的一端连接晶振的其中一个频率引脚。 芯片时钟信号输出脚:电阻的另一端连接微控制器的时钟输出引脚(OSC_…时间:2025/04/06 -

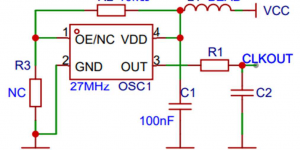

; ) 有源晶振需要串联电阻吗?

有源晶振需要串联电阻吗? 答:在有源晶振应用电路中,一般不需要串联电阻。 如上图所示: 当发生信号反射或/及信号完整性受损时,可以尝试增加一个低阻值串联电阻,选值一般为几十欧姆,如20~50欧姆。时间:2024/09/05

有源晶振需要串联电阻吗?

有源晶振需要串联电阻吗? 答:在有源晶振应用电路中,一般不需要串联电阻。 如上图所示: 当发生信号反射或/及信号完整性受损时,可以尝试增加一个低阻值串联电阻,选值一般为几十欧姆,如20~50欧姆。时间:2024/09/05 -

; ) 在晶振匹配测试,激励功率大了会怎样?

(晶振过驱后,频率发生不稳定现象) 在晶振匹配测试,激励功率大了会怎样? 答:如果芯片提供了过大的激励功率给晶振,意味着可能发生“过驱”问题。具体表现为晶振发烫、工作不稳定或使用寿命缩短。 在无源晶振规格书中,都会明确注明晶振的激励功率的典型值和最大值两个参数。如下图所示: 如果晶振存在“过驱”现象…时间:2024/08/02

在晶振匹配测试,激励功率大了会怎样?

(晶振过驱后,频率发生不稳定现象) 在晶振匹配测试,激励功率大了会怎样? 答:如果芯片提供了过大的激励功率给晶振,意味着可能发生“过驱”问题。具体表现为晶振发烫、工作不稳定或使用寿命缩短。 在无源晶振规格书中,都会明确注明晶振的激励功率的典型值和最大值两个参数。如下图所示: 如果晶振存在“过驱”现象…时间:2024/08/02 -

; ) 25MHz晶振输出串联电阻是多大?

25MHz晶振输出串联电阻是多大? 答:在无源晶振电路实际应用中,如果不存在晶振被芯片过驱问题,一般情况下不需要增加串联电阻。 关于晶振的等效串联电阻和(电路中)串联电阻的区别 等效串联电阻(ESR): 无源晶振本身电气参数之一(意思是:相当于在电路中串联了一个电阻的大小),该值的大小因晶振封装尺寸…时间:2024/07/19

25MHz晶振输出串联电阻是多大?

25MHz晶振输出串联电阻是多大? 答:在无源晶振电路实际应用中,如果不存在晶振被芯片过驱问题,一般情况下不需要增加串联电阻。 关于晶振的等效串联电阻和(电路中)串联电阻的区别 等效串联电阻(ESR): 无源晶振本身电气参数之一(意思是:相当于在电路中串联了一个电阻的大小),该值的大小因晶振封装尺寸…时间:2024/07/19 -

; ) 晶振是否需要串联电阻?

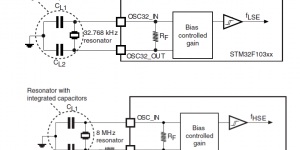

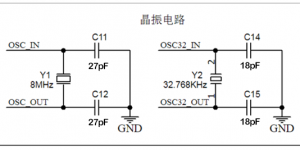

晶振是否需要串联电阻? 答:32.768KHz无源晶振电路不需要串联电阻;MHz无源晶振电路,只有在过驱(激励功率过大)的情况下才串联几十Ω的电阻。在没有过驱的情况下,也无需串联电阻。 如下图所示: 32.768KHz晶体谐振器与8MHz晶体谐振器典型振荡电路时间:2024/07/02

晶振是否需要串联电阻?

晶振是否需要串联电阻? 答:32.768KHz无源晶振电路不需要串联电阻;MHz无源晶振电路,只有在过驱(激励功率过大)的情况下才串联几十Ω的电阻。在没有过驱的情况下,也无需串联电阻。 如下图所示: 32.768KHz晶体谐振器与8MHz晶体谐振器典型振荡电路时间:2024/07/02 -

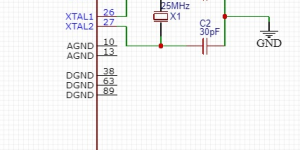

; ) 8MHz晶振匹配电容是22pF还是20pF?

8MHz晶振匹配电容是22pF还是20pF? 答:8MHz晶振的匹配电容具体是多少pF是由其本身电气参数负载电容(CL)及所在电路板上的杂散电容(Cs)共同决定的。 (8MHz无源晶振电路应用范例) 一般情况下,我们把电路板上的杂散电容(Cs)按照3~5pF计算的话,晶诺威科技建议如下: 如果所选8…时间:2024/02/27

8MHz晶振匹配电容是22pF还是20pF?

8MHz晶振匹配电容是22pF还是20pF? 答:8MHz晶振的匹配电容具体是多少pF是由其本身电气参数负载电容(CL)及所在电路板上的杂散电容(Cs)共同决定的。 (8MHz无源晶振电路应用范例) 一般情况下,我们把电路板上的杂散电容(Cs)按照3~5pF计算的话,晶诺威科技建议如下: 如果所选8…时间:2024/02/27 -

; ) 数字电路中信号异常及可能原因

关于数字电路中信号异常及可能原因,晶诺威科技归纳如下: 1、幅值异常 波形不稳定,导致无法判定高低电平。 可能原因: 负载太大 走线过长 驱动太小 电平异常 2、过冲/回冲 方波过冲/回冲过高。超出正常电平10%。 可能原因: 驱动过高 存在反射 自激振荡 检查去耦 避免晶体振荡器输出波形失真的对策…时间:2023/12/13

数字电路中信号异常及可能原因

关于数字电路中信号异常及可能原因,晶诺威科技归纳如下: 1、幅值异常 波形不稳定,导致无法判定高低电平。 可能原因: 负载太大 走线过长 驱动太小 电平异常 2、过冲/回冲 方波过冲/回冲过高。超出正常电平10%。 可能原因: 驱动过高 存在反射 自激振荡 检查去耦 避免晶体振荡器输出波形失真的对策…时间:2023/12/13 -

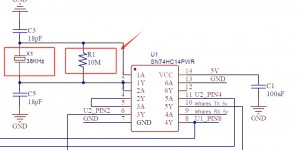

; ) 无源晶振电路是并联1MΩ电阻还是10M电阻?

(晶诺威科技产38KHz无源晶振并联10MΩ反馈电阻电路) 无源晶振电路是并联1MΩ电阻还是10M电阻? 答:晶诺威科技建议MHz无源晶振并联1MΩ电阻,而KHz无源晶振并联10MΩ电阻。 (晶诺威科技产8MHz无源晶振并联1MΩ R2反馈电阻电路) 注:该电阻为无源晶振电路的RF反馈电阻,建议保留…时间:2023/11/19

无源晶振电路是并联1MΩ电阻还是10M电阻?

(晶诺威科技产38KHz无源晶振并联10MΩ反馈电阻电路) 无源晶振电路是并联1MΩ电阻还是10M电阻? 答:晶诺威科技建议MHz无源晶振并联1MΩ电阻,而KHz无源晶振并联10MΩ电阻。 (晶诺威科技产8MHz无源晶振并联1MΩ R2反馈电阻电路) 注:该电阻为无源晶振电路的RF反馈电阻,建议保留…时间:2023/11/19 -

; ) 如何检测无源晶振过驱?晶振过驱怎么办?

如何检测晶振过驱?晶振过驱怎么办?晶诺威科技建议如下: 晶振过驱测量方法 给电路板正常通电后,借助示波器来检测晶振频率输出脚: 如果检测到非常清晰的正弦波,且正弦波的上限值和下限值都符合时钟输入需要,则晶振未被过分驱动; 如果正弦波形的波峰,波谷两端被削平,而使波形成为方形,则晶振被过分驱动。这时就…时间:2023/08/15

如何检测无源晶振过驱?晶振过驱怎么办?

如何检测晶振过驱?晶振过驱怎么办?晶诺威科技建议如下: 晶振过驱测量方法 给电路板正常通电后,借助示波器来检测晶振频率输出脚: 如果检测到非常清晰的正弦波,且正弦波的上限值和下限值都符合时钟输入需要,则晶振未被过分驱动; 如果正弦波形的波峰,波谷两端被削平,而使波形成为方形,则晶振被过分驱动。这时就…时间:2023/08/15