-

; ) 晶振是信号中的干扰源吗?

晶振是信号中的干扰源吗? 答:无源晶振本身不是干扰源,但由其产生的时钟信号及其电路设计不当,很容易成为系统中最主要的电磁干扰源之一。 关于该问题,晶诺威科技分析如下: 1、 无源晶振的本质:一个高Q值谐振器 无源晶振(晶体谐振器)本身是一个被动、高精度的频率基准元件。它利用石英晶体的压电效应,在特定…时间:2026/03/04

晶振是信号中的干扰源吗?

晶振是信号中的干扰源吗? 答:无源晶振本身不是干扰源,但由其产生的时钟信号及其电路设计不当,很容易成为系统中最主要的电磁干扰源之一。 关于该问题,晶诺威科技分析如下: 1、 无源晶振的本质:一个高Q值谐振器 无源晶振(晶体谐振器)本身是一个被动、高精度的频率基准元件。它利用石英晶体的压电效应,在特定…时间:2026/03/04 -

; ) 关于网口晶振25MHz/50MHz辐射超标问题的建议

(晶振辐射超标) 网口EMC辐射超标是硬件设计中非常经典的难题。它的根源往往是一个“干扰源”加上一条“发射天线”的组合——板上的高频噪声(比如晶振的谐波)通过网口这个路径,以共模电流的形式耦合到网线上,而网线本身就是一根高效的 antenna,将噪声辐射出去。 简单来说,网口晶振(如:25MHz/5…时间:2025/11/13

关于网口晶振25MHz/50MHz辐射超标问题的建议

(晶振辐射超标) 网口EMC辐射超标是硬件设计中非常经典的难题。它的根源往往是一个“干扰源”加上一条“发射天线”的组合——板上的高频噪声(比如晶振的谐波)通过网口这个路径,以共模电流的形式耦合到网线上,而网线本身就是一根高效的 antenna,将噪声辐射出去。 简单来说,网口晶振(如:25MHz/5…时间:2025/11/13 -

; ) 关于“辐射不是由晶振直接造成”的解释

关于“辐射不是由晶振直接造成”的解释如下: 晶振个体较小,它直接影响的是近场辐射(表现为晶振与其他导体(如参考接地板)之间形成的寄生电容),造成远场辐射的直接因素是电缆或产品中最大尺寸与辐射频率波长可以比拟的导体;此外,将晶振外壳接地可以在一定程度上减少这种干扰叠加到系统上。 时钟晶体和相关电路应布…时间:2025/05/25

关于“辐射不是由晶振直接造成”的解释

关于“辐射不是由晶振直接造成”的解释如下: 晶振个体较小,它直接影响的是近场辐射(表现为晶振与其他导体(如参考接地板)之间形成的寄生电容),造成远场辐射的直接因素是电缆或产品中最大尺寸与辐射频率波长可以比拟的导体;此外,将晶振外壳接地可以在一定程度上减少这种干扰叠加到系统上。 时钟晶体和相关电路应布…时间:2025/05/25 -

; ) 电子设计中的EMI和EMC有什么区别?

(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele…时间:2024/06/10

电子设计中的EMI和EMC有什么区别?

(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele…时间:2024/06/10 -

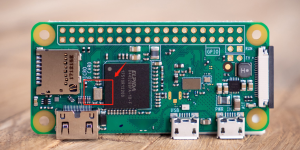

; ) Crystal Oscillator PCB Layout Guidelines for Design

(Crystal Oscillator PCB Layout Guidelines for Design) When using a crystal oscillator in your PCB design, remember that it is very EMI sensitive and m…时间:2024/04/25

Crystal Oscillator PCB Layout Guidelines for Design

(Crystal Oscillator PCB Layout Guidelines for Design) When using a crystal oscillator in your PCB design, remember that it is very EMI sensitive and m…时间:2024/04/25 -

; ) 8MHz无源晶振典型应用电路说明(中英文)

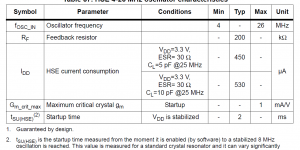

关于8MHz无源晶振典型应用电路说明,晶诺威科技解释如下: 以STM32F为例:HSE 4-26 MHz oscillator characteristics The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz…时间:2024/04/17

8MHz无源晶振典型应用电路说明(中英文)

关于8MHz无源晶振典型应用电路说明,晶诺威科技解释如下: 以STM32F为例:HSE 4-26 MHz oscillator characteristics The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz…时间:2024/04/17 -

; ) 关于晶振应用常见问题及实际案例分析

关于晶振应用常见问题及实际案例,晶诺威科技总结并分析如下: 晶振型号选择不当 案例:某设计团队在开发一款高性能通信设备时,为节省成本,选择了无源晶振作为时钟源。然而,在测试过程中发现,设备的信号质量较差,通信性能无法达到预期。 解决方案:分析问题原因,发现由于无源晶振频率稳定性较差,导致通信性能不佳…时间:2023/08/23

关于晶振应用常见问题及实际案例分析

关于晶振应用常见问题及实际案例,晶诺威科技总结并分析如下: 晶振型号选择不当 案例:某设计团队在开发一款高性能通信设备时,为节省成本,选择了无源晶振作为时钟源。然而,在测试过程中发现,设备的信号质量较差,通信性能无法达到预期。 解决方案:分析问题原因,发现由于无源晶振频率稳定性较差,导致通信性能不佳…时间:2023/08/23 -

; ) 金属封装4脚无源晶振2号引脚和4号引脚的作用

关于金属封装4脚无源晶振2号引脚和4号引脚的作用,说明如下: The metal package with pin #2 & #4 case ground acts as shielding to minimize radiation. 晶诺威科技产金属封装无源晶振2号引脚和4号引脚(与金属…时间:2023/05/03

金属封装4脚无源晶振2号引脚和4号引脚的作用

关于金属封装4脚无源晶振2号引脚和4号引脚的作用,说明如下: The metal package with pin #2 & #4 case ground acts as shielding to minimize radiation. 晶诺威科技产金属封装无源晶振2号引脚和4号引脚(与金属…时间:2023/05/03 -

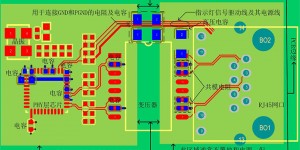

; ) 晶振抗干扰电路:电源,信号线,GND及隔离区设计说明

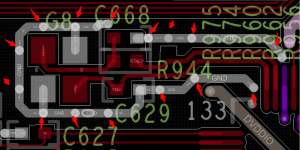

(晶振抗干扰电路:关于电源,信号线,GND及隔离区图示) 晶振抗干扰电路设计时,请注意以下六点: 1、在晶振布线时,尽量将晶振靠近芯片方式、缩短布线长度,匹配电容也一样 2、晶振走线要直 3、晶振走线不能有过孔 4、晶振位置不要靠近高压,大电流的电源走线 5、有源晶振一般比无源晶振抗干扰能力更强,因…时间:2022/05/31

晶振抗干扰电路:电源,信号线,GND及隔离区设计说明

(晶振抗干扰电路:关于电源,信号线,GND及隔离区图示) 晶振抗干扰电路设计时,请注意以下六点: 1、在晶振布线时,尽量将晶振靠近芯片方式、缩短布线长度,匹配电容也一样 2、晶振走线要直 3、晶振走线不能有过孔 4、晶振位置不要靠近高压,大电流的电源走线 5、有源晶振一般比无源晶振抗干扰能力更强,因…时间:2022/05/31 -

; ) 晶诺威科技产有源晶振EMI消除方案

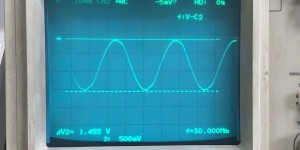

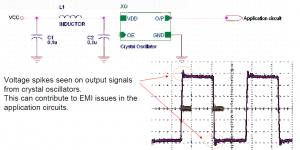

晶诺威科技产有源晶振EMI消除方案解释如下: 1、由下图可见有源晶振输出信号中出现电压尖峰,这可能会给应用电路带来EMI问题。如下图所示: 2、晶诺威科技建议在时钟信号输出端和 GND 之间添加旁路电容( 5-10 pF ),可以使输出波形平滑化,并可显著降低EMI。如下图所示:时间:2022/04/27

晶诺威科技产有源晶振EMI消除方案

晶诺威科技产有源晶振EMI消除方案解释如下: 1、由下图可见有源晶振输出信号中出现电压尖峰,这可能会给应用电路带来EMI问题。如下图所示: 2、晶诺威科技建议在时钟信号输出端和 GND 之间添加旁路电容( 5-10 pF ),可以使输出波形平滑化,并可显著降低EMI。如下图所示:时间:2022/04/27