晶振是信号中的干扰源吗?

答:无源晶振本身不是干扰源,但由其产生的时钟信号及其电路设计不当,很容易成为系统中最主要的电磁干扰源之一。

关于该问题,晶诺威科技分析如下:

1、 无源晶振的本质:一个高Q值谐振器

无源晶振(晶体谐振器)本身是一个被动、高精度的频率基准元件。它利用石英晶体的压电效应,在特定频率上产生机械共振。作为一个独立的元件,它不主动产生干扰。

2、 真正的“干扰源”:时钟信号和振荡电路

我们通常说的“晶振干扰”,实际上指的是:

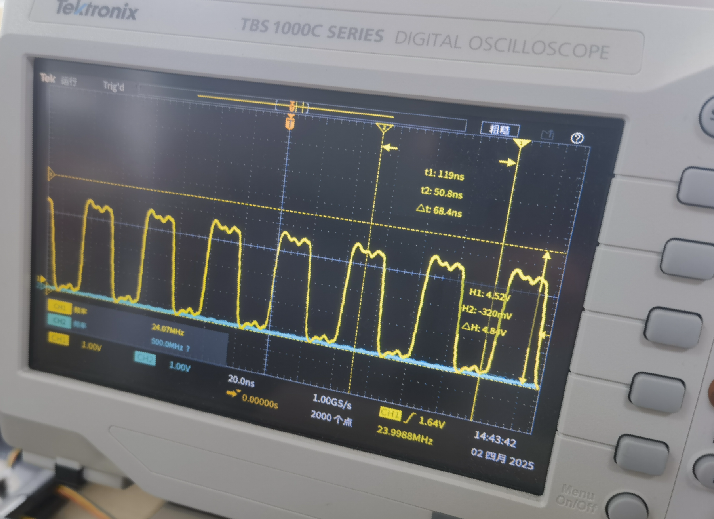

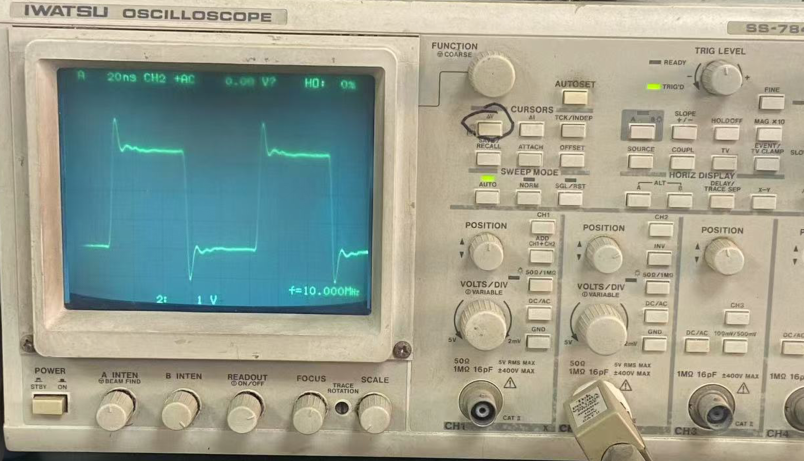

- 高频时钟信号本身:晶振(通常是振荡器模块,如OSC)输出的是一个频率稳定、边沿陡峭(上升/下降时间短)的方波信号。这个信号包含了丰富的高次谐波;

- 驱动电路:振荡器内部或外部的反相器、驱动电路在切换状态时,会产生瞬间的电流尖峰;

- 不良的PCB设计:这是导致干扰问题最常见的原因。

3、 晶振电路如何成为干扰源?

- 谐波辐射

理想的方波是由基波和无数奇次谐波(3次、5次、7次…)组成的。一个25MHz的方波,其谐波可以延伸到数百MHz甚至GHz。这些高频分量很容易通过PCB走线、元件引脚等像天线一样辐射出去,干扰其他电路或设备。

- 地弹和电源噪声

时钟驱动器瞬间切换时,会从电源抽取大电流,在电源和地平面的阻抗上产生电压波动(噪声),这个噪声会耦合到其他共用同一电源的芯片上。

- 电流回路面积过大

如果晶振的负载电容回路、或晶振到芯片的时钟走线回路面积很大,会形成一个高效的环形天线,加剧电磁辐射。

- 串扰

如果时钟信号线过长,或与其他敏感信号线(如模拟线、复位线)平行走线且距离过近,会通过容性耦合或感性耦合将噪声耦合过去。

4、 如何判断和解决“晶振干扰”?

在EMC测试(如RE辐射发射测试)中,如果频谱图上出现以晶振频率为间隔的“梳状”尖峰,基本可以确定是时钟信号及其谐波引起的干扰。

通用的解决方案(PCB布局和布线准则):

1、缩短走线

尽可能将晶振/振荡器靠近主芯片(如MCU、CPU)的时钟引脚放置。

2、减小回路面积

- 为晶振提供一个完整、局部的接地平面。

- 对于两脚的无源晶体,其两个负载电容的接地端应分别通过最短的路径就近下地(via to GND plane)。

- 时钟信号线下面要有连续的参考地平面。

3、远离敏感电路

让晶振和时钟走线远离模拟电路、天线、高频信号线、复位电路等。

4、使用屏蔽

在要求极高的场合,可以为晶振加上金属屏蔽罩。

5、选择合适器件

- 在满足系统时序要求的前提下,选择上升/下降时间稍缓的振荡器(但不要过慢,否则可能引起时序问题)。

- 考虑使用展频时钟。这是一种主动技术,通过轻微调制时钟频率,将单个频率的尖峰能量分散到一个频带内,从而显著降低峰值辐射。

- 对于无源晶体,使用推荐的负载电容值,并确保电容的ESR/ESL小,且布线对称。

6、电源滤波

在振荡器或主芯片的电源引脚处,靠近引脚放置一个高频性能好的去耦电容(如100nF + 10pF组合)。

因此,在电路设计和PCB布局时,必须将晶振及其时钟信号作为高风险信号进行特殊处理,否则它极有可能成为整个系统的“干扰之源”。