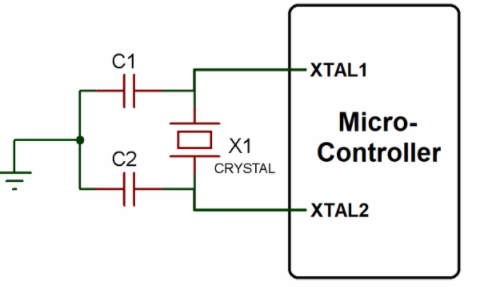

(无源晶振应用电路)

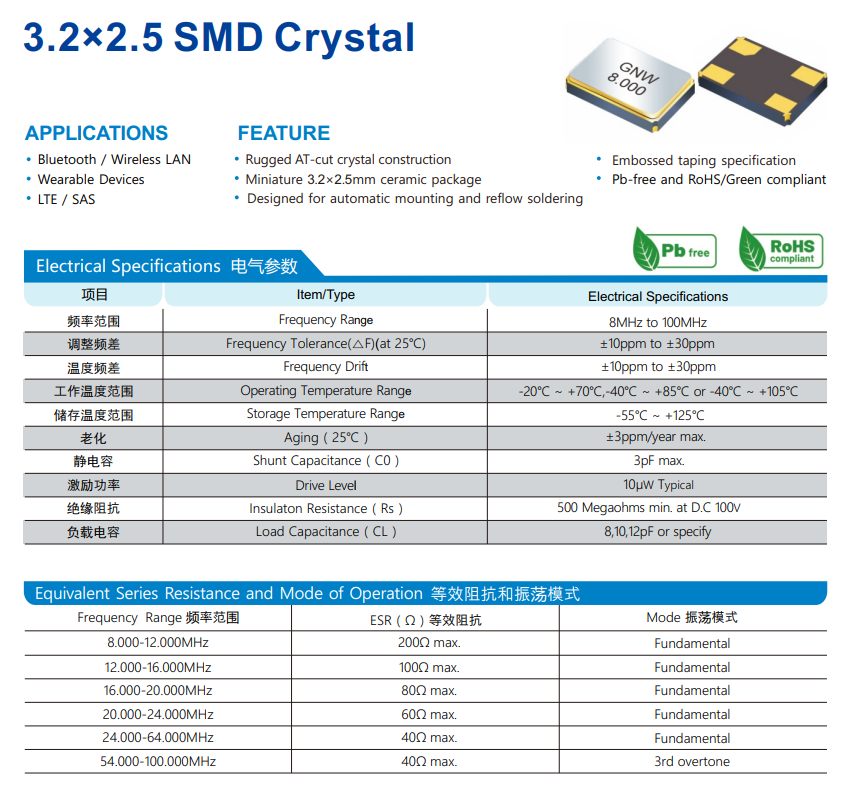

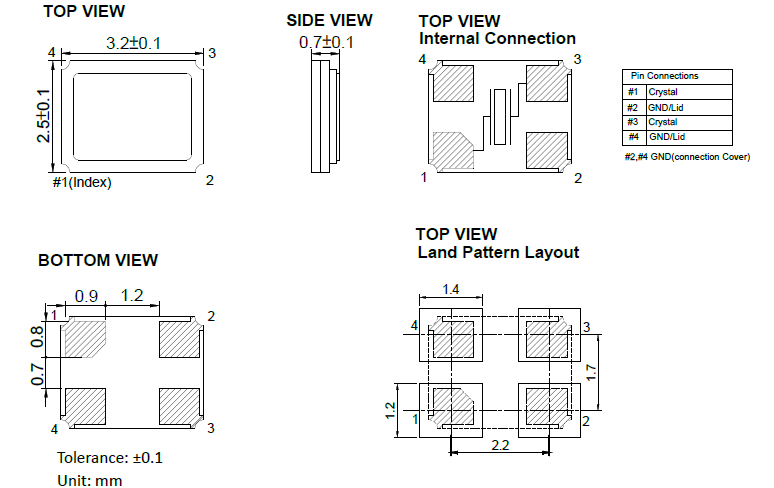

在无源晶振使用中,首先是选对晶振封装尺寸及规格参数。封装尺寸是由电路板给晶振预留空间所决定,另外还有焊盘数量及尺寸。

关于晶振的主要规格参数,一般指的是晶振的频率精度与负载电容。电子设备具备什么功直接决定着对晶振精度的选择,比如蓝牙、WIFI功能,频率精度至少为±10PPM,而定位功能若要实现高精准化,晶振的精度越高越好,有高要求的方案采用精度在±0.2PPM以上的有源温补晶振TCXO。

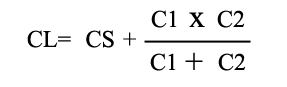

一谈及电容计算,显然指的就是无源晶振。在晶振选型已经确定及晶振品质合格的条件下,晶振外接电容选值就是面临的首要问题。

晶振选型的确认,意味着晶振的负载电容已经固定。负载电容越大,意味着功耗越大。反之,晶振的负载越小,则功耗越小。因此,小负载晶振是便携式低功耗数码电子产品之首选。

(无源晶振匹配电容计算公式)

注:

1、CL:无源晶振本身的电气参数—负载电容。

2、CS:指杂散电容,包括IC内部的杂散容值、电路板布线间的电容量、PCB板各层之间的寄生电容等。杂散电容CS一般按照3~5PF来估算。

3、C1和C2指无源晶振频率输出脚与输入脚的外接(对地)电容。

以上无源晶振电容计算公式仅作为理论上的参考使用。基于无源晶振在实际振荡电路应用中受到电路设计及杂散电容等多方面影响,建议上电测试晶振实际输出频率,为晶振选择最佳电容,这样才能确保晶振输出频率的精度。

拓展阅读:晶振电容应靠近晶振引脚还是MCU引脚放置?

这是PCB布局中高频易被忽视却影响起振可靠性的关键问题。实践中常见错误是将两个负载电容(如22pF)对称布设在晶振与MCU之间,或刻意靠近MCU引脚以“缩短到芯片的距离”。但根据EMI抑制原理和寄生参数建模,电容必须紧邻晶振两端(即并联在XTAL/XTAL1引脚之间),且走线越短、越粗、越对称越好。

原因:

晶振为高阻抗谐振器件,其等效串联电阻(ESR)极小,任何引线电感(>0.5nH/mm)都会与电容形成额外LC谐振,导致相位裕度下降、起振延迟甚至停振;而MCU端引脚内部已集成反相放大器及缓冲结构,对电容位置不敏感。实测表明,电容距晶振>3mm时,-40℃低温起振失败率可升高5~10倍。

正确做法:

电容焊盘直接打孔紧贴晶振焊盘,禁用过孔换层,且避开电源/数字走线干扰区。