-

; ) 有源晶振输出方波变形成振铃怎么解决?

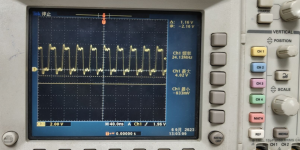

有源晶振输出方波变形成振铃怎么解决? 有源晶振输出方波变形成振铃通常不是一个故障,而是信号完整性问题的典型表现。晶诺威科技详解如下: 一、 什么是“振铃”? 振铃是指方波信号在跳变沿(上升沿或下降沿)后,出现的一系列幅度逐渐衰减的振荡,形状类似于铃铛被敲击后的声音波形,因此得名。 正常的理想方波: …时间:2026/03/07

有源晶振输出方波变形成振铃怎么解决?

有源晶振输出方波变形成振铃怎么解决? 有源晶振输出方波变形成振铃通常不是一个故障,而是信号完整性问题的典型表现。晶诺威科技详解如下: 一、 什么是“振铃”? 振铃是指方波信号在跳变沿(上升沿或下降沿)后,出现的一系列幅度逐渐衰减的振荡,形状类似于铃铛被敲击后的声音波形,因此得名。 正常的理想方波: …时间:2026/03/07 -

; ) 无源晶振和有源晶振如何连入电路?

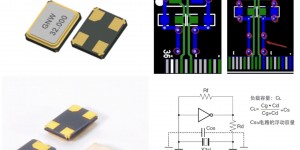

无源晶振和有源晶振如何连入电路?晶诺威科技解释如下: About circuit connection 关于电路连接 The output level of Crystal is variable, and it depends on the vibration of the circuit. Th…时间:2023/12/28

无源晶振和有源晶振如何连入电路?

无源晶振和有源晶振如何连入电路?晶诺威科技解释如下: About circuit connection 关于电路连接 The output level of Crystal is variable, and it depends on the vibration of the circuit. Th…时间:2023/12/28 -

; ) 石英晶振的作用、基本工作原理与电路设计

关于石英晶振的作用、基本工作原理与电路设计,晶诺威科技总结如下: 石英晶振是一种高精度、高稳定度的振荡器,是利用石英晶体的压电效应而制成的谐振组件,以取代LC 选频电路,广泛应用于各类电子产品的振荡电路中,如通信系统中的频率发生器等。 石英晶振的作用: 为数据处理设备产生时钟信号,提供系统振荡脉冲,…时间:2023/10/09

石英晶振的作用、基本工作原理与电路设计

关于石英晶振的作用、基本工作原理与电路设计,晶诺威科技总结如下: 石英晶振是一种高精度、高稳定度的振荡器,是利用石英晶体的压电效应而制成的谐振组件,以取代LC 选频电路,广泛应用于各类电子产品的振荡电路中,如通信系统中的频率发生器等。 石英晶振的作用: 为数据处理设备产生时钟信号,提供系统振荡脉冲,…时间:2023/10/09 -

; ) 造成晶振频偏超差原因,频偏引发的不良影响及解决方案

关于造成晶振频偏超差的原因,晶诺威科技归纳四点如下: 晶振本身电气参数不稳定 晶振的品质因子(Q值)和频率稳定性系数(Δf/f)是影响频率偏差的主要参数。低品质的晶振容易产生较大的频率偏差。 晶振工作环境因素 温度、湿度、气压等环境因素会影响晶体的机械特性,从而导致频率偏差。其中,温度是最主要的影响…时间:2023/05/05

造成晶振频偏超差原因,频偏引发的不良影响及解决方案

关于造成晶振频偏超差的原因,晶诺威科技归纳四点如下: 晶振本身电气参数不稳定 晶振的品质因子(Q值)和频率稳定性系数(Δf/f)是影响频率偏差的主要参数。低品质的晶振容易产生较大的频率偏差。 晶振工作环境因素 温度、湿度、气压等环境因素会影响晶体的机械特性,从而导致频率偏差。其中,温度是最主要的影响…时间:2023/05/05 -

; ) 晶振的作用及晶振电路PCB设计

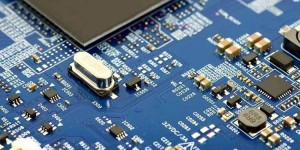

关于晶振的作用及晶振电路PCB设计,晶诺威科技介绍如下: 晶振的作用 一个数字电路就像一个城市的交通,晶振的作用就是十字路口的信号灯。数字电路又像生命体,它的运行就像人身体里的血液流通,它不是由单一的某个器件或器件单元构成,而是由多个器件及程序彼此配合、协调,共同完成良性的运转。晶振电路由晶振和相关…时间:2023/03/14

晶振的作用及晶振电路PCB设计

关于晶振的作用及晶振电路PCB设计,晶诺威科技介绍如下: 晶振的作用 一个数字电路就像一个城市的交通,晶振的作用就是十字路口的信号灯。数字电路又像生命体,它的运行就像人身体里的血液流通,它不是由单一的某个器件或器件单元构成,而是由多个器件及程序彼此配合、协调,共同完成良性的运转。晶振电路由晶振和相关…时间:2023/03/14 -

; ) 不合理的PCB设计也可能造成晶振不起振

不合理的PCB设计也可能造成晶振不起振,归纳五点建议如下: 1、若无源晶振距离板边太近,则易导致晶振辐射杂讯或超声波焊接破坏,建议离PCB板边10mm以上。晶振位置不合理设计,如下面两图所示: (图一) (图二) 2、无源晶振电路尽可能地靠近芯片的时钟管脚放…时间:2023/01/03

不合理的PCB设计也可能造成晶振不起振

不合理的PCB设计也可能造成晶振不起振,归纳五点建议如下: 1、若无源晶振距离板边太近,则易导致晶振辐射杂讯或超声波焊接破坏,建议离PCB板边10mm以上。晶振位置不合理设计,如下面两图所示: (图一) (图二) 2、无源晶振电路尽可能地靠近芯片的时钟管脚放…时间:2023/01/03 -

; ) 为何晶振的时钟电路要优先设计?

我们都知道,构建一套完整且正确的数字电路需要做出很多复杂的步骤。为了实现某些特定的功能及性能,我们除了选取合适的电子元件以外,还要考虑如何以最佳的方案把它们构建在一起。那么,何时是一个最佳的时间来解决时钟信号的问题呢?换句话说,晶体谐振器或晶体振荡器是优先考虑还是放在最后再考虑呢? 晶诺威科技认为在…时间:2022/10/09

为何晶振的时钟电路要优先设计?

我们都知道,构建一套完整且正确的数字电路需要做出很多复杂的步骤。为了实现某些特定的功能及性能,我们除了选取合适的电子元件以外,还要考虑如何以最佳的方案把它们构建在一起。那么,何时是一个最佳的时间来解决时钟信号的问题呢?换句话说,晶体谐振器或晶体振荡器是优先考虑还是放在最后再考虑呢? 晶诺威科技认为在…时间:2022/10/09 -

; ) 晶振下方可以走线吗?

晶振下方可以走线吗? 答:不可以! 晶振下方不可以走线。另外,晶振布放和走线同IC应在相同层(走线过程不能隔断,不要过孔换层)。时钟线路尽量短,防止形成发射天线,引发信号之间干扰。时间:2022/07/19

晶振下方可以走线吗?

晶振下方可以走线吗? 答:不可以! 晶振下方不可以走线。另外,晶振布放和走线同IC应在相同层(走线过程不能隔断,不要过孔换层)。时钟线路尽量短,防止形成发射天线,引发信号之间干扰。时间:2022/07/19 -

; ) 晶振选型及电路应用注意事项归纳

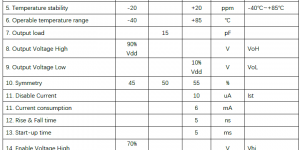

关于晶振选型及电路应用需要注意事项,晶诺威科技归纳如下: 标称频率(Nominal Frequency) 如果PCBA上的芯片设计方案已经确定,则必须选择与之相配的标称频率晶振,否则将导致系统不工作。 负载电容(CL) 首先确认选择的是无源晶振,那么要根据芯片方案所需晶振负载参数,选择对应负载电容参…时间:2022/04/28

晶振选型及电路应用注意事项归纳

关于晶振选型及电路应用需要注意事项,晶诺威科技归纳如下: 标称频率(Nominal Frequency) 如果PCBA上的芯片设计方案已经确定,则必须选择与之相配的标称频率晶振,否则将导致系统不工作。 负载电容(CL) 首先确认选择的是无源晶振,那么要根据芯片方案所需晶振负载参数,选择对应负载电容参…时间:2022/04/28

; )