不合理的PCB设计也可能造成晶振不起振,归纳五点建议如下:

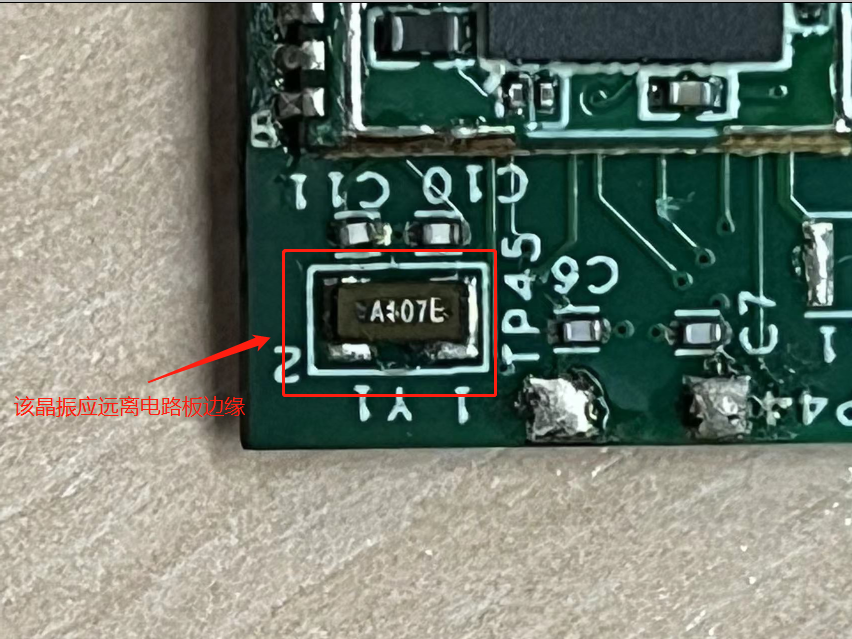

1、若无源晶振距离板边太近,则易导致晶振辐射杂讯或超声波焊接破坏,建议离PCB板边10mm以上。晶振位置不合理设计,如下面两图所示:

(图一)

(图二)

2、无源晶振电路尽可能地靠近芯片的时钟管脚放置,布线尽可能的短,以减少走线的负载电容和防止不必要的噪声。

3、时钟信号走线Xin和Xout以及无源晶振下方第二层需要是完整的地平面做隔离,投影区域建议禁止任何走线,避免噪声耦合进入时钟电路。

4、无源晶振电路围绕放置地环。地环通过过孔与相邻的接地层连接,以隔离噪声,如果芯片有晶振的模拟地,需要单独地孔到平面。

5、无源晶振的两个负载电容要靠近该无源晶振的两个频率引脚,信号先经过后再到主芯片。有源晶振的滤波电容应尽量靠近该有源晶振的电源引脚,位置摆放顺序:按电源流入方向,依容值从大到小依次摆放,容值最小的电容最靠近电源引脚。