关于晶振不易起振或振荡不稳定原因之晶振负载电容不匹配,晶诺威科技解释如下:

晶体元件的负载电容是指在电路中跨接晶体两端的总的外界有效电容。它是晶振要正常振荡所需要的电容。一般外接电容,是为了使晶振两端的等效电容等于或接近负载电容。要求高的场合还要考虑IC输入端的对地电容。应用时一般在给出负载电容值附近调整可以得到精确频率。此电容的大小主要影响负载谐振频率和等效负载谐振电阻。

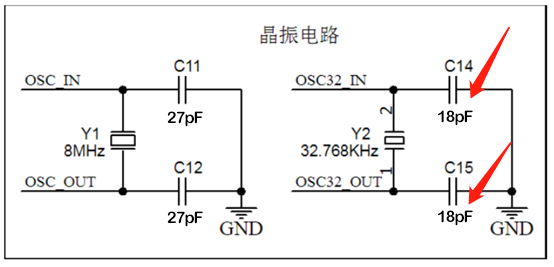

晶振的负载电容=[(Cd*Cg)/(Cd+Cg)] +Cic+△C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C(PCB上的电容)。如果晶振的负载电容等于20pF的话,晶诺威科技建议两边各接27pF~33pF,一般杂散电容为3~5pF。

注:

杂散电容,又称为寄生电容或分布电容,是指电子电路中不经意间产生的电容效应。在晶振电路中,杂散电容主要来源于电路板上的导线、元器件之间的绝缘不完全或元件间距过小等因素。这些电容虽然微小,但却会对晶振的性能产生显著影响。

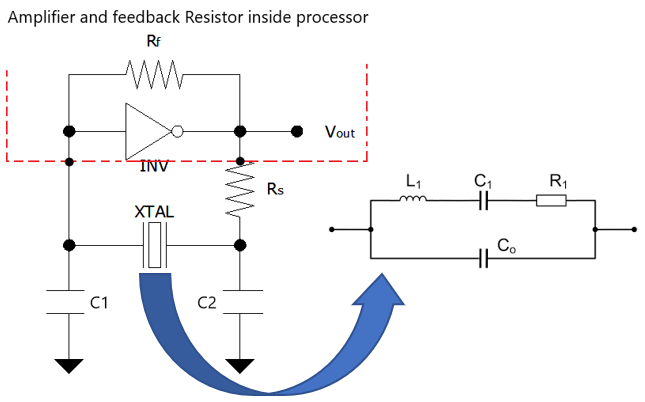

各种逻辑芯片的晶振引脚可以等效为电容三点式振荡器。

晶振引脚的内部通常是一个反相器,或者是奇数次的反相器串联。 在晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接,对于CMOS 芯片通常是数 M 到数十 M 欧之间。 很多芯片的引脚内部已经包含了这个电阻,引脚外部无需再接。 该电阻是为了使反相器在振荡初始时处与线性状态。

反相器就如同一个有很大增益的放大器,以便于起振。 石英晶体也连接在晶振引脚的输入和输出之间,等效为一个并联谐振回路,振荡频率应该等同于石英晶体的并联谐振频率。晶体旁边的两个电容接地,实际上就是电容三点式电路的分压电容,接地点就是分压点。 以接地点即分压点为参考点,振荡引脚的输入和输出是反相的,但从并联谐振回路即石英晶体两端来看,形成一个正反馈以保证电路持续振荡。

在芯片设计时,这两个电容就已经形成了,一般是两个容量相等,容量大小依工艺和版图而不同,但终归是比较小,不一定适合很宽的频率范围。 外接时大约是数 PF 到数十 PF,依频率和石英晶体的特性而定。

需要注意的是:这两个电容串联的值是并联在谐振回路上的,会影响振荡频率。 当两个电容量相等时,反馈系数是0.5,一般是可以满足振荡条件。 如果不易起振或振荡不稳定,我们可以减小输入端对地电容量,借此来增加输出端的值以提高反馈量。