近年来,基于即时视频传输越来越受到广泛需求,网络通信的大量数据的非延时性传输与交换问题也随之展现在我们眼前。在这种情况下,高速通信基站对高频且输出信号稳定的基准信号源的需求已经迫在眉睫。通常,从MHz频带的AT型晶振获得高频振荡时需要将石英片加工得很薄,因为AT型石英晶体的频率因其厚度而定。这就造成在加工工艺、机械性强度和容易起振等方面存在局限。现今,晶振以基波起振高频时的上限为60MHz左右。

近年来,基于即时视频传输越来越受到广泛需求,网络通信的大量数据的非延时性传输与交换问题也随之展现在我们眼前。在这种情况下,高速通信基站对高频且输出信号稳定的基准信号源的需求已经迫在眉睫。通常,从MHz频带的AT型晶振获得高频振荡时需要将石英片加工得很薄,因为AT型石英晶体的频率因其厚度而定。这就造成在加工工艺、机械性强度和容易起振等方面存在局限。现今,晶振以基波起振高频时的上限为60MHz左右。

从技术层面讲,晶振输出稳定且高频基准频率信号并不容易,下面介绍四种方法:

第一种

使用基准频率为20MHz 的AT切晶片,利用倍频电路或锁相环(PLL)电路输出稳定的高频基准信号。

第二种

使用表面声波SAW谐振器输出高频基准信号,表面声波SAW谐振器利用弹性表面声波(SAW:Surface Acoustic Wave)以基波直接起振高频。

第三种

制造出仅将振动部分加工变薄的AT切晶片,以此产生稳定的高频基准信号。

第四种

使用AT切晶片的高频振动的振动模式(谐波)输出稳定的高频基准信号。

具体原理如下:

1、输出N倍高频的倍频电路

倍频电路是指把某一频率的电气信号转换为N倍高频的电路。一般的振荡电路输出信号具有一定的Tr、Tf、Voh和Vol时,其波形中将包含高谐波成份。倍频电路利用这些高谐波产生有意加强了N次成份的信号,并用滤波器抽出N次成份。由于使用高谐波,因此可以获得抖动小于锁相环电路的输出频率。然而,若欲只抽出N次高谐波,则要求在选择石英晶体单元和设计起振电路时加以注意。例如需要使用频带窄、高衰减的带通滤波器(BPF),把N/2次以下的分谐波衰减掉,以便抑制抖动;还要使输入信号在N次高谐波附近不带噪音(失真)等。因此,为了得到高频,产品中大多使用锁相环电路。

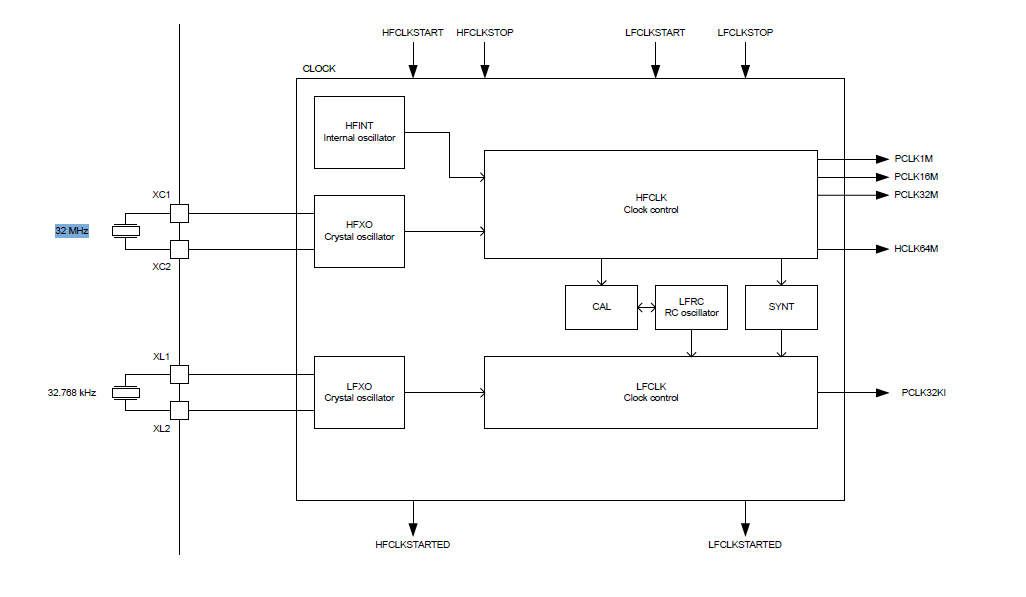

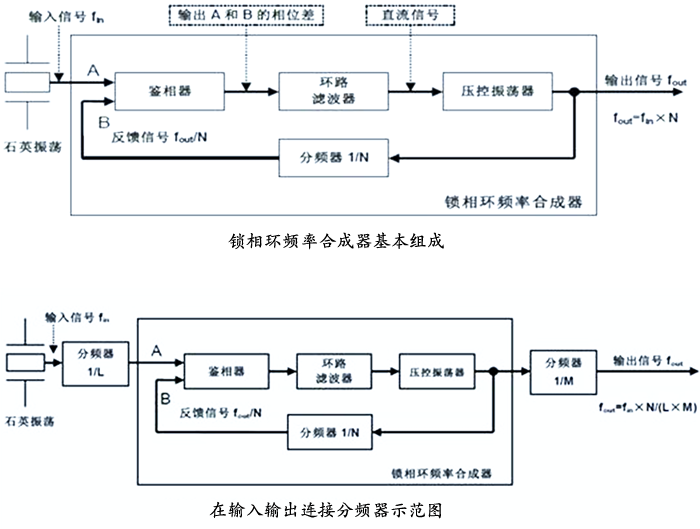

2、锁相环电路

晶振锁相环电路产生与输入的基准信号相同步的输出信号。该电路的基本组成是鉴相器、环路滤波器和压控振荡器(VCXO)。它将正确地产生与输入信号相同步的信号。与倍频电路不同的是,锁相环电路不直接使用输入信号制作输出信号。在锁相环电路中,由压控振荡器(VCXO)产生与输入信号相同频率的同步信号。

在锁相环电路的压控振荡器输出和鉴相器的输入之间连接分频器,通过使输入信号与分频后的信号相同步,从而将压控振荡器的输出频率控制在分频倍数的频率。使用石英晶体振荡器等能够产生稳定频率,并转换分频器的分频数,就能使压控振荡器的输出达到石英晶体振荡器同等精度且等于分频倍数频率的信号。这就是频率合成器的原理。

通过利用该原理,把AT切晶振输出的MHz频带频率输入到锁相环频率合成器,就能够产生用于无线通信的GHz频带载波信号。

使用锁相环频率合成器获得大于输入频率几倍的频率时,分频器的使用方法是关键。

为了提高锁相环频率合成器的频率设定分辨率,通常把分频器直接连接在石英晶体振荡器。但是,若为了提高频率设定分辨率而取较大的分频数,则将造成用于比较相位的频率变小,引发锁相环响应慢、环路增益下降的可能性,并对输出波形的抖动和相位噪音特性造成不良影响。为解决上述问题,也可使用小数分频锁相环。

3、整数分频锁相环与小数分频锁相环的特征

锁相环电路可分为整数分频和小数分频两大类。双方均利用波源输出高频。

整数分频锁相环可以名副其实地产生输入频率整数倍的输出频率。例如,希望从1MHz的波源获得100MHz的输出时,分频器的计数器设定值为100。

小数分频锁相环可以产生输入频率小数倍的输出频率。这意味着可以任意选择频率,即能够获得微小的频率设定分辨率。它可以获得微小的频率分辨率,发挥这个特征可以对初始频率公差进行精密控制。然而,小数分频的电路设计复杂,集成电路面积也比整数分频大,因此容易造成失真问题,致使小数分频的相位噪音与整数分频相比较差。令人欣慰的是,随着近几年科研技术的发展,小数分频锁相环获得不断改善。

※ 获得高频输出的倍频和锁相环电路需要注意事项:

1、倍频电路:应注意分谐波混入电路以及因 N/2 以下成份而引起的抖动。

2、锁相环电路:应注意环路频带,在锁相环电路之后串联其它锁相环电路时应注意抖动增幅及变化。