-

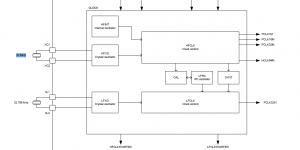

; ) ±0.28ppm高精度低相噪锁相晶振PLL-TCXO2012-10pin规格参数

关于±0.28ppm高精度低相噪锁相晶振PLL-TCXO2012-10pin规格参数,晶诺威科技说明如下: 1、产品特点: 支持外部信号参考源 输出类型(可选):正弦波Sine Wave、方波CMOS 高精度(±0.28ppm)、低相噪、低抖动 SMD贴片式封装 20.2*12.6mm 工作温度:-…时间:2025/11/03

±0.28ppm高精度低相噪锁相晶振PLL-TCXO2012-10pin规格参数

关于±0.28ppm高精度低相噪锁相晶振PLL-TCXO2012-10pin规格参数,晶诺威科技说明如下: 1、产品特点: 支持外部信号参考源 输出类型(可选):正弦波Sine Wave、方波CMOS 高精度(±0.28ppm)、低相噪、低抖动 SMD贴片式封装 20.2*12.6mm 工作温度:-…时间:2025/11/03 -

; ) 关于爱普生可编程晶振SG-8002 PLL锁相环电路说明

关于爱普生可编程晶振SG-8002 PLL锁相环电路,晶诺威科技解释如下: The SG-8002 series contains a PLL circuit and there are a few cases where the jitter value may be increased when…时间:2025/01/11

关于爱普生可编程晶振SG-8002 PLL锁相环电路说明

关于爱普生可编程晶振SG-8002 PLL锁相环电路,晶诺威科技解释如下: The SG-8002 series contains a PLL circuit and there are a few cases where the jitter value may be increased when…时间:2025/01/11 -

; ) 蓝牙(Bluetooth)是如何工作的?

How Does Bluetooth Work? 蓝牙是如何工作的? Bluetooth technology uses a wavelength to transmit information; however, it only works over short distances. You ma…时间:2024/06/11

蓝牙(Bluetooth)是如何工作的?

How Does Bluetooth Work? 蓝牙是如何工作的? Bluetooth technology uses a wavelength to transmit information; however, it only works over short distances. You ma…时间:2024/06/11 -

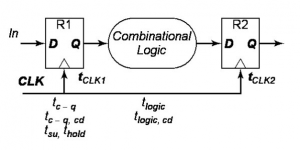

; ) 时钟偏差/倾斜Clock Skew与VCXO压控晶振的Voltage Control

Clock Skew是影响时钟信号稳定性的主要因素之一。 若VCXO额定输入电压为5V,当实际输入电压为2.5V时,晶振输出频率为中心频率。 电源的表现形式也可看做为波形的一种。当占空比为0时,实质为直流电。在VCXO实际工作中,由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有…时间:2022/07/07

时钟偏差/倾斜Clock Skew与VCXO压控晶振的Voltage Control

Clock Skew是影响时钟信号稳定性的主要因素之一。 若VCXO额定输入电压为5V,当实际输入电压为2.5V时,晶振输出频率为中心频率。 电源的表现形式也可看做为波形的一种。当占空比为0时,实质为直流电。在VCXO实际工作中,由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有…时间:2022/07/07 -

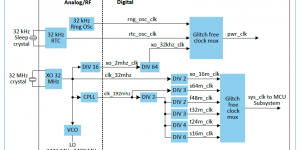

; ) 关于时钟信号分频,倍频和锁相环PLL电路

关于时钟信号分频,倍频和锁相环PLL电路相关知识,晶诺威科技整理如下: 锁相环振荡器(PLL): 锁相环是一种反馈控制系统,它可以将输入信号的相位锁定到晶振产生的输出信号上。每种振荡器的设计和应用都有其特定的要求,选择合适的驱动方式取决于所需的频率稳定性、功耗、尺寸、成本和应用场合。在设计和应用时,…时间:2022/07/06

关于时钟信号分频,倍频和锁相环PLL电路

关于时钟信号分频,倍频和锁相环PLL电路相关知识,晶诺威科技整理如下: 锁相环振荡器(PLL): 锁相环是一种反馈控制系统,它可以将输入信号的相位锁定到晶振产生的输出信号上。每种振荡器的设计和应用都有其特定的要求,选择合适的驱动方式取决于所需的频率稳定性、功耗、尺寸、成本和应用场合。在设计和应用时,…时间:2022/07/06 -

; ) 晶振标称频率与锁相环PLL倍频原理

(锁相环PLL倍频原理) 晶振为MCU提供其执行命令时所需的时钟信号,而晶振的标称频率则是用来专门描述这种周期性的输出频率。 晶振标称频率与石英晶片的厚度,面积,切割方式有关,晶片越薄则频率越高。由于生产工艺的限制,晶片不能无限的薄,否则会存在破裂的风险。为了提高晶振的频率,晶振制造中可以采用泛音振…时间:2021/10/30

晶振标称频率与锁相环PLL倍频原理

(锁相环PLL倍频原理) 晶振为MCU提供其执行命令时所需的时钟信号,而晶振的标称频率则是用来专门描述这种周期性的输出频率。 晶振标称频率与石英晶片的厚度,面积,切割方式有关,晶片越薄则频率越高。由于生产工艺的限制,晶片不能无限的薄,否则会存在破裂的风险。为了提高晶振的频率,晶振制造中可以采用泛音振…时间:2021/10/30 -

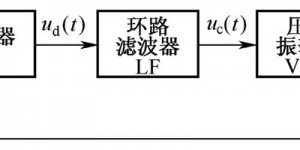

; ) 晶振锁相环电路原理介绍

近年来,基于即时视频传输越来越受到广泛需求,网络通信的大量数据的非延时性传输与交换问题也随之展现在我们眼前。在这种情况下,高速通信基站对高频且输出信号稳定的基准信号源的需求已经迫在眉睫。通常,从MHz频带的AT型晶振获得高频振荡时需要将石英片加工得很薄,因为AT型石英晶体的频率因其厚度…时间:2020/07/18

晶振锁相环电路原理介绍

近年来,基于即时视频传输越来越受到广泛需求,网络通信的大量数据的非延时性传输与交换问题也随之展现在我们眼前。在这种情况下,高速通信基站对高频且输出信号稳定的基准信号源的需求已经迫在眉睫。通常,从MHz频带的AT型晶振获得高频振荡时需要将石英片加工得很薄,因为AT型石英晶体的频率因其厚度…时间:2020/07/18