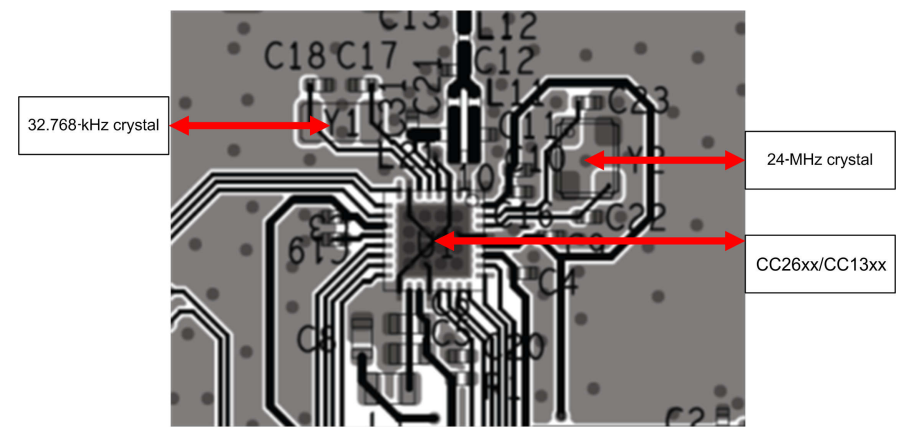

如何最大程度减少晶振电路中的串扰信号及EMI?晶诺威科技解答如下:

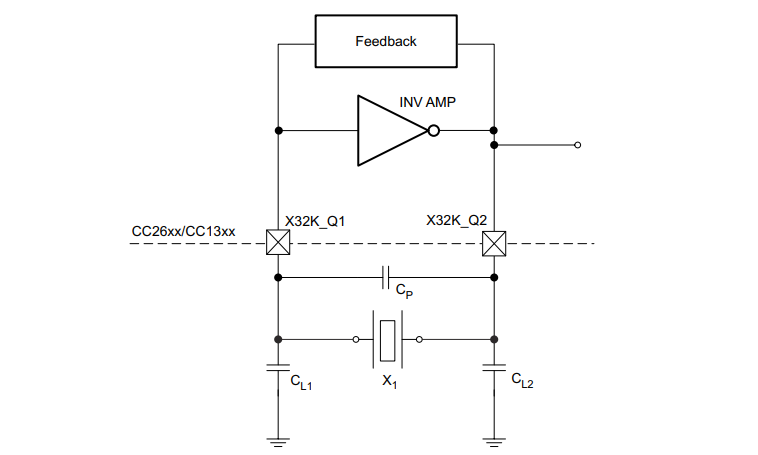

( Low-Frequency Oscillator with Quartz Crystal 32.768KHz)

As is shown above,The oscillator circuit consists of an inverting amplifier, a feedback net, capacitors, and a crystal.The 32.768 KHz crystal lacks internal capacitors and requires external loading capacitors.

如上图所示:振荡器电路由以下部分组成:反相放大器、反馈网、电容器和晶体32.768KHz。32.768KHz晶体缺少内部电容,因此需要外接负载电容。

The layout of the crystal can reduce the parasitic capacitance and, more importantly, reduce noise from coupling on the input of the oscillators. Noise on the input of the oscillator can lead to severe side effects such as clock glitches, flash corruption, or system crashes because most of the smart digital devices rely on the crystal oscillators as the high- and low-frequency system clock.

晶体谐振器(无源晶振)的布局可以减少寄生电容,更重要的是,可以减少振荡器输入端的耦合噪声。由于当前大部分数码智能电子产品依赖晶体振荡器作为高频和低频系统时钟,因此振荡器输入端的噪声可能导致严重的副作用,例如时钟故障、闪存损坏或系统崩溃。

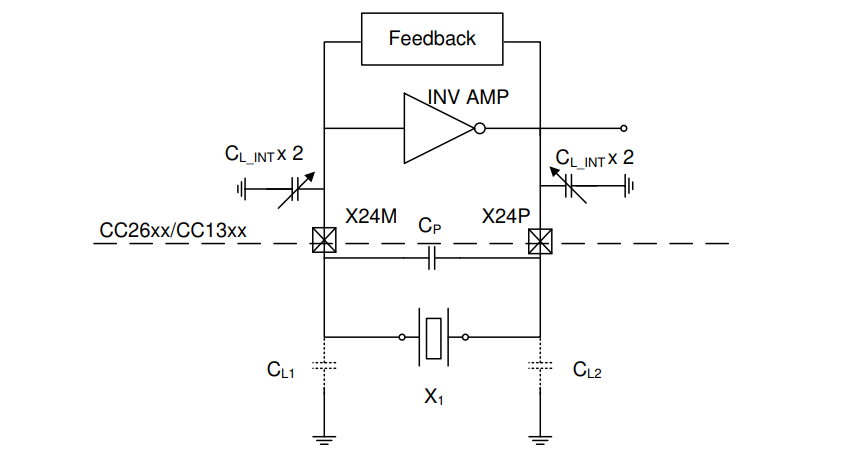

(High-Frequency Oscillator With Quartz Crystal 24MHz)

If no external capacitors are used then the value of CL is determined by the internal loading capacitors plus board parasitic capacitance CP.

如果不使用外部电容,则晶振负载CL值由内部负载电容加板寄生电容CP构成。

The following are a few recommendations for the layout of the crystals以下是关于晶体布局的一些建议:

1、 Place the crystal as close as possible to the device to minimize the length of the PCB traces. (This placement reduces crosstalk and minimizes EMI.)

将晶体谐振器尽可能靠近芯片时钟信号引脚,以减少 PCB 迹线的长度。(这种布局可以减少串扰并最大程度减少EMI。)

2、 Genuway recommends a solid ground plane under the crystal.

晶诺威强烈建议在晶体下方创建一个接地平面。

3、 Ensure no high-speed digital signals are close to the crystal to minimize cross-coupling of noise into the oscillator.

确保没有高速数字信号靠近晶体,借此以最大程度减少将噪声耦合到振荡器。

晶振选型注意事项:

1、Size (footprint area and height) 尺寸(焊盘及高度)

2、Performance (accuracy over temperature, lifetime, power consumption, and start-up time) 性能(频率温度稳定性、使用寿命、功耗和启动时间)

3、Capacitive loading and frequency tolerance must meet the specifications of the standard used (for example, Blue tooth low energy).电容负载和频率容差必须符合所用标准的规格(用于例如,蓝牙低功耗)。

4、ESR must not be greater than can be driven by the device. ESR(等效电阻)不得大于芯片所能驱动的ESR。

5、Confrim if Anti-ultrasonic crystal oscillators should be selected. 确认是否需要选择抗超声波晶振产品。