体谐振器动态电容C1的大小对频偏有什么影响?

答:晶体谐振器的动态电容(C1)是影响其频率稳定性和频偏(频率偏移)的关键参数之一。它与晶体的等效电路模型密切相关。

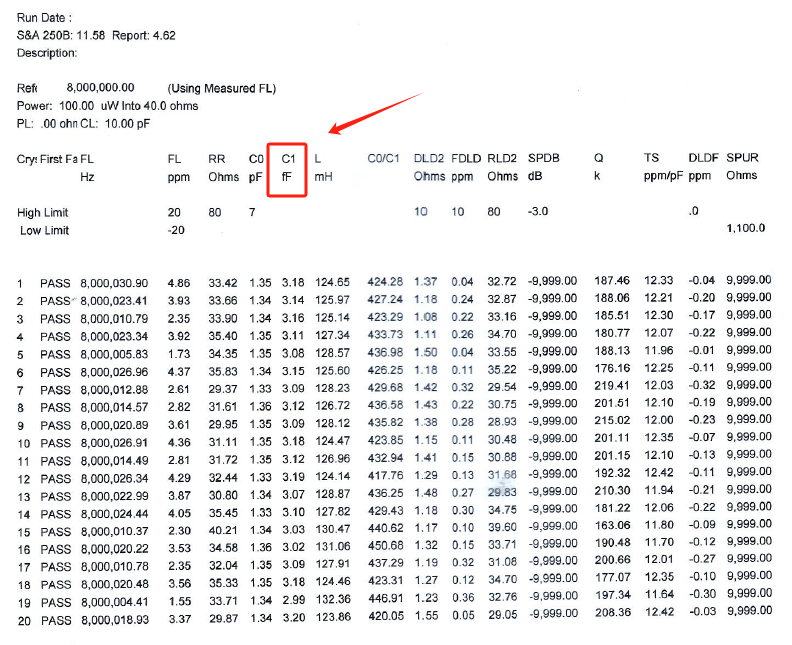

(动态电容C1测试数据:SMD3225无源贴片晶振8MHz 10pF ±20ppm)

关于晶体谐振器动态电容C1的大小对频偏的影响,晶诺威科技具体分析如下:

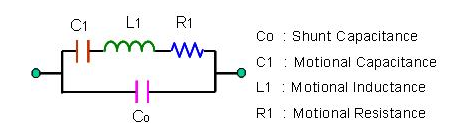

1、 动态电容(C1)的定义

在晶体的等效电路中,动态电容 (C1) 是串联谐振支路中的电容,代表晶体振动时的弹性性能。它与动态电感( L1) 和动态电阻 (R1) 共同构成串联谐振回路。

2、 动态电容对频率的影响

晶体的谐振频率(串联谐振频率 (fs) 和并联谐振频率 (fp)由( L1) 和 (CL) 决定。

动态电容 (CL) 的变化会直接改变 (fs) 和 (fp):

(C1) 增大 → (fs) 和(fp) 降低。

(C1) 减小 → (fs) 和(fp) 升高。

3、 动态电容与频偏的关系

频偏(如温度漂移、负载变化等导致的频率偏移)可能由 (C1) 的变化引起:

1) 温度变化的影响

晶体的弹性常数(等效为 (C1)会随温度变化,尤其是非温补晶振(如普通无源晶振)。

例如:AT切晶体在常温下 (C1) 较稳定,但在高温或低温时 (C1) 可能变化,导致频偏。

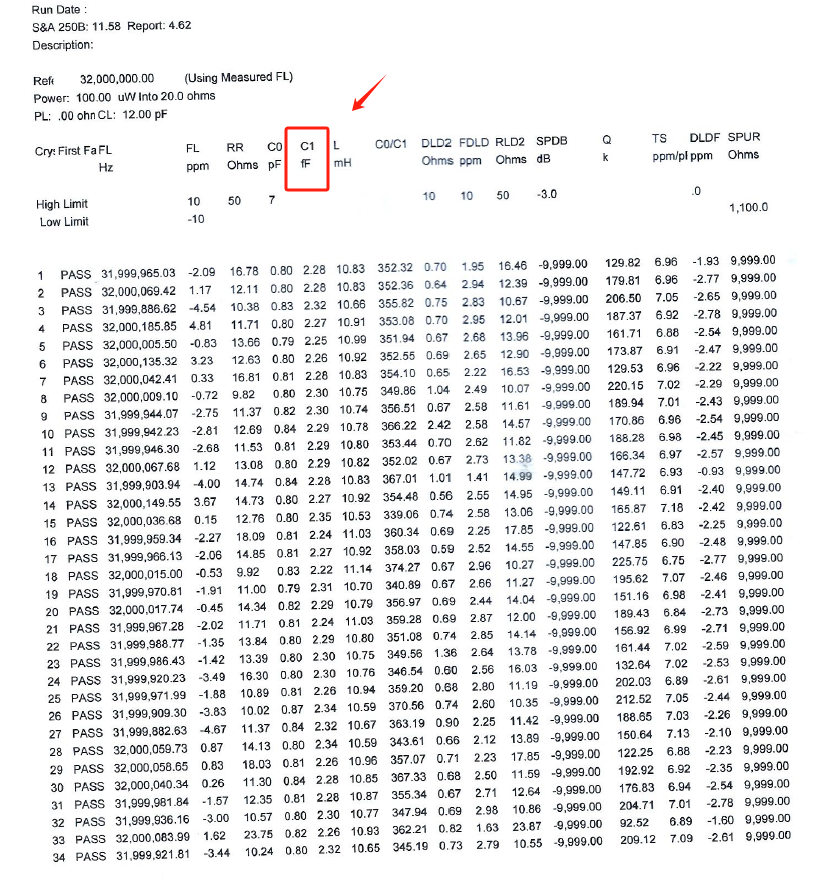

2) 负载电容的匹配

实际电路中,晶体的负载电容 (CL) 需与设计值匹配。若 (CL) 偏离标称值,会导致振荡频率偏移:

动态电容 (C1) 越大,相同的 (CL) 偏差引起的频偏越显著。因此,高 (C1) 的晶体对负载电容更敏感。

3) 老化效应

晶体长期使用后,电极或材料特性变化可能导致 (C1) 缓慢变化,引发长期频偏。

(动态电容C1测试数据:SMD2016无源贴片晶振32MHz 12pF ±10ppm)

4、实际设计中的应对措施

1)选择低 (C1) 的晶体:

低 (C1) 晶体对负载电容变化不敏感,频偏更小(但需权衡起振难度)。

2)严格匹配负载电容 (CL) :

根据晶体规格书调整外部电容 (CL) ,使CL = C0 + C电路。

3)使用温补晶振(TCXO)或恒温晶振(OCXO):

通过温度补偿电路或恒温环境抑制 (C1) 的温度漂移。

4)控制PCB布局:

减少寄生电容(如缩短走线),避免引入额外的 (C1) 干扰。

总结

1)动态电容 (C1) 是晶体频率的核心参数,其变化会直接导致频偏。

2)频偏敏感度:高 (C1) 的晶体对负载电容、温度、老化的敏感性更高。

3)设计关键:通过选型、负载匹配和环境控制来最小化 (C1) 的影响。

若频偏问题严重,建议用网络分析仪或晶体测试仪测量 (C1)、(C0) 的实际值,并检查电路匹配是否合理。