-

; ) 电源会影响到晶振正常工作吗?

电源会影响到晶振正常工作吗? 答:会的!电源电压的变化会对晶振性能产生影响。 解释如下: 晶振作为电子设备中的关键元件,其性能直接影响到设备的稳定性和可靠性。因此在电源设计时,要保证电源电压的稳定性,采用合适的稳压器、滤波器等元件,降低电源电压波动对晶振的影响。时间:2023/07/04

电源会影响到晶振正常工作吗?

电源会影响到晶振正常工作吗? 答:会的!电源电压的变化会对晶振性能产生影响。 解释如下: 晶振作为电子设备中的关键元件,其性能直接影响到设备的稳定性和可靠性。因此在电源设计时,要保证电源电压的稳定性,采用合适的稳压器、滤波器等元件,降低电源电压波动对晶振的影响。时间:2023/07/04 -

; ) 电路板上的杂散信号对晶振的影响是什么?

电路板上的杂散信号对晶振的影响是什么? 答:造成干扰,引发信号失真。 关于电路板杂散超差带来的问题,晶诺威科技解释如下: 杂散信号可能会通过晶振引脚或周边电路传导,干扰其它电子元件的正常工作。尤其是在高频应用中,这种干扰可能导致晶振信号失真、通信错误或其它性能问题。 若晶振信号受到干扰,这对于要求高…时间:2023/07/03

电路板上的杂散信号对晶振的影响是什么?

电路板上的杂散信号对晶振的影响是什么? 答:造成干扰,引发信号失真。 关于电路板杂散超差带来的问题,晶诺威科技解释如下: 杂散信号可能会通过晶振引脚或周边电路传导,干扰其它电子元件的正常工作。尤其是在高频应用中,这种干扰可能导致晶振信号失真、通信错误或其它性能问题。 若晶振信号受到干扰,这对于要求高…时间:2023/07/03 -

; ) 负载电容CL=12PF时24MHz晶振匹配电容选多大?

负载电容CL=12PF时24MHz晶振匹配电容选多大? 答:建议15~18PF。 解释说明: 关于CL=12PF时晶振匹配电容选值的具体大小,请使用频率计数器以晶振实际输出频偏为依据进行调整,调整逻辑为反比关系。24MHz晶振PPM值与频偏范围对照如下: ±10PPM:23.999760MHz~24…时间:2023/07/02

负载电容CL=12PF时24MHz晶振匹配电容选多大?

负载电容CL=12PF时24MHz晶振匹配电容选多大? 答:建议15~18PF。 解释说明: 关于CL=12PF时晶振匹配电容选值的具体大小,请使用频率计数器以晶振实际输出频偏为依据进行调整,调整逻辑为反比关系。24MHz晶振PPM值与频偏范围对照如下: ±10PPM:23.999760MHz~24…时间:2023/07/02 -

; ) 若芯片只有XIN却没有XOUT接晶振的哪个脚?

若芯片只有XIN却没有XOUT接晶振的哪个脚? 答:若芯片只有XIN(信号输入脚)却没有XOUT(信号输出脚),很可能说明该芯片采用的为有源晶振方案,而不是常见的无源晶振皮尔斯振荡电路方案(除非是少见的密勒振荡电路)。 解决方案: 请选择有源晶振(晶体振荡器)。基本原理是:给有源晶振提供额定电压,将…时间:2023/06/29

若芯片只有XIN却没有XOUT接晶振的哪个脚?

若芯片只有XIN却没有XOUT接晶振的哪个脚? 答:若芯片只有XIN(信号输入脚)却没有XOUT(信号输出脚),很可能说明该芯片采用的为有源晶振方案,而不是常见的无源晶振皮尔斯振荡电路方案(除非是少见的密勒振荡电路)。 解决方案: 请选择有源晶振(晶体振荡器)。基本原理是:给有源晶振提供额定电压,将…时间:2023/06/29 -

; ) 晶振49S/49SMD封装DLD不良可能引发晶振不稳定问题

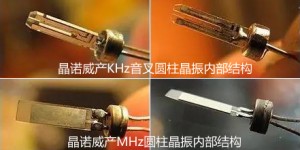

关于晶振49S/49SMD封装DLD不良可能引发晶振不稳定问题,晶诺威科技解析如下: 作为研发并制造石英晶体谐振器的专业厂家,我们就是要为客户提供质优价廉的可靠产品。但实际上经常还会有些产品在电路应用中出现故障,主要症状为三个: 频偏 停振 不稳定 晶振产品在客户端一旦出现问题,客户就会要求我们尽快…时间:2023/06/26

晶振49S/49SMD封装DLD不良可能引发晶振不稳定问题

关于晶振49S/49SMD封装DLD不良可能引发晶振不稳定问题,晶诺威科技解析如下: 作为研发并制造石英晶体谐振器的专业厂家,我们就是要为客户提供质优价廉的可靠产品。但实际上经常还会有些产品在电路应用中出现故障,主要症状为三个: 频偏 停振 不稳定 晶振产品在客户端一旦出现问题,客户就会要求我们尽快…时间:2023/06/26 -

; ) 蜂鸣器会干涉晶振正常工作吗?

蜂鸣器会干涉晶振正常工作吗? 答:是的,会干扰晶振正常工作。 解释说明如下: 因为晶振为频率元件,其工作原理是由内部石英晶片高频振动产生我们所需的高精度高稳定性频率信号,因此附近产生高频振动的设备(类似Buzzer/蜂鸣器、horn/喇叭及Stepper motor/步进电机等)都会干扰晶振正常工作…时间:2023/06/25

蜂鸣器会干涉晶振正常工作吗?

蜂鸣器会干涉晶振正常工作吗? 答:是的,会干扰晶振正常工作。 解释说明如下: 因为晶振为频率元件,其工作原理是由内部石英晶片高频振动产生我们所需的高精度高稳定性频率信号,因此附近产生高频振动的设备(类似Buzzer/蜂鸣器、horn/喇叭及Stepper motor/步进电机等)都会干扰晶振正常工作…时间:2023/06/25 -

; ) 晶振跌落后如何处理?

关于晶振跌落问题,晶诺威科技解释如下: Our crystal products are designed and manufactured to resist physical shocks. However, in the event the crystal is subjected to ex…时间:2023/06/23

晶振跌落后如何处理?

关于晶振跌落问题,晶诺威科技解释如下: Our crystal products are designed and manufactured to resist physical shocks. However, in the event the crystal is subjected to ex…时间:2023/06/23 -

; ) 关于晶振故障原因分析及应对方法

关于晶振故障原因分析及应对方法,晶诺威科技解释如下: 了解晶振故障可能导致的不良现象 晶振故障导致的不良现象包括:设备无法正常启动、射频类设备联机失败、无线传输数据丢失、晶振频率不稳定、晶振频偏超差、晶振高低温停振、晶振输出信号幅度衰减等。 测量晶振实际输出频率 给电路板上电,使用频率计数器或示波器…时间:2023/06/21

关于晶振故障原因分析及应对方法

关于晶振故障原因分析及应对方法,晶诺威科技解释如下: 了解晶振故障可能导致的不良现象 晶振故障导致的不良现象包括:设备无法正常启动、射频类设备联机失败、无线传输数据丢失、晶振频率不稳定、晶振频偏超差、晶振高低温停振、晶振输出信号幅度衰减等。 测量晶振实际输出频率 给电路板上电,使用频率计数器或示波器…时间:2023/06/21 -

; ) 在没有外接电容的情况下无源晶振输出频率偏负怎么调?

在没有外接电容的情况下无源晶振输出频率偏负怎么调? 答:建议尝试较大负载电容CL的晶振或选择内置补偿电容的芯片。 在无源晶振起振电路中,我们通常通过改变其外接电容的大小来调节其输出频率的高低。在无源晶振没有外接电容的方案中,晶振发生频偏较大的问题,我们建议电子工程师仔细阅读芯片数据手册中该晶振相关内…时间:2023/06/21

在没有外接电容的情况下无源晶振输出频率偏负怎么调?

在没有外接电容的情况下无源晶振输出频率偏负怎么调? 答:建议尝试较大负载电容CL的晶振或选择内置补偿电容的芯片。 在无源晶振起振电路中,我们通常通过改变其外接电容的大小来调节其输出频率的高低。在无源晶振没有外接电容的方案中,晶振发生频偏较大的问题,我们建议电子工程师仔细阅读芯片数据手册中该晶振相关内…时间:2023/06/21 -

; ) 若晶振输出频偏为正,外接匹配电容是减小还是增大?

若晶振输出频偏为正,外接匹配电容是减小还是增大? 答:若实测无源晶振输出频率为正(偏快)的话,建议适当增加外接电容值。规律:外接电容增大,频率下降;外接电容减小,频率上升。 (上电测试,40MHz晶振输出频率偏负31.75ppm) 举例:如果原来外接电容为22PF,建议先增加至27PF,然后上电测试…时间:2023/06/21

若晶振输出频偏为正,外接匹配电容是减小还是增大?

若晶振输出频偏为正,外接匹配电容是减小还是增大? 答:若实测无源晶振输出频率为正(偏快)的话,建议适当增加外接电容值。规律:外接电容增大,频率下降;外接电容减小,频率上升。 (上电测试,40MHz晶振输出频率偏负31.75ppm) 举例:如果原来外接电容为22PF,建议先增加至27PF,然后上电测试…时间:2023/06/21