-

; ) 晶振功耗过大解决办法有哪些?

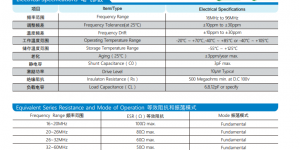

(无源晶振SMD2016电气参数) 晶振功耗过大解决办法有哪些? 答:一般情况下,晶振体积越小,功耗越小。 如果是有源晶振应用方案,直接选择低功耗有源晶振系列就好了。如果是无源晶振方案,建议选择低负载(CL)及低等效电阻(ESR)。 (有源晶振OSC7050电气参数) 晶诺威科技详解如下: 1、在有…时间:2024/08/26

晶振功耗过大解决办法有哪些?

(无源晶振SMD2016电气参数) 晶振功耗过大解决办法有哪些? 答:一般情况下,晶振体积越小,功耗越小。 如果是有源晶振应用方案,直接选择低功耗有源晶振系列就好了。如果是无源晶振方案,建议选择低负载(CL)及低等效电阻(ESR)。 (有源晶振OSC7050电气参数) 晶诺威科技详解如下: 1、在有…时间:2024/08/26 -

; ) 怎么判定芯片需要多大频率晶振?

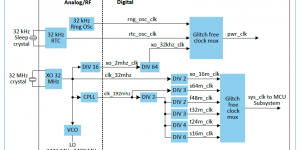

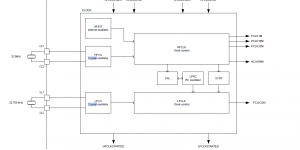

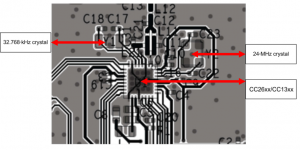

(EXTERNAL CRYSTAL:外部晶振) 怎么判定芯片需要多大频率晶振? 答:根据芯片型号,查阅芯片手册关于外部时钟相关内容。 如下图所示: 该型号芯片需要两颗外部晶振,频率分别为32MHz和32.768KHz。时间:2024/08/25

怎么判定芯片需要多大频率晶振?

(EXTERNAL CRYSTAL:外部晶振) 怎么判定芯片需要多大频率晶振? 答:根据芯片型号,查阅芯片手册关于外部时钟相关内容。 如下图所示: 该型号芯片需要两颗外部晶振,频率分别为32MHz和32.768KHz。时间:2024/08/25 -

; ) Specification and test data for Crystal SMD3225 32MHz 8pF 10ppm

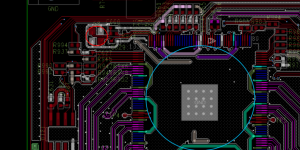

(Crystal 32MHz and 32.768KHz on Bluetooth PCBA) Specification for Crystal SMD3225 32MHz 8pF 10ppm Test data for Crystal SMD3225 32MHz 8pF 10ppm Frequ…时间:2024/08/24

Specification and test data for Crystal SMD3225 32MHz 8pF 10ppm

(Crystal 32MHz and 32.768KHz on Bluetooth PCBA) Specification for Crystal SMD3225 32MHz 8pF 10ppm Test data for Crystal SMD3225 32MHz 8pF 10ppm Frequ…时间:2024/08/24 -

; ) 四脚无源贴片晶振焊盘图解:XTAL,NC 还是 GND?

脚无源贴片晶振焊盘说明:XTAL,NC 还是 GND?晶诺威科技说明如下: 案例一:如上图所示: 1、晶振尺寸为:3.2mm*2.5mm 2、焊盘有缺角标识的为#4脚,对角方向为#2脚。NC:NO CONNECTION,中文意思是:不连接。 3、#1脚和#3脚与内部晶片电路相连,为频率管脚,不具备方…时间:2024/08/23

四脚无源贴片晶振焊盘图解:XTAL,NC 还是 GND?

脚无源贴片晶振焊盘说明:XTAL,NC 还是 GND?晶诺威科技说明如下: 案例一:如上图所示: 1、晶振尺寸为:3.2mm*2.5mm 2、焊盘有缺角标识的为#4脚,对角方向为#2脚。NC:NO CONNECTION,中文意思是:不连接。 3、#1脚和#3脚与内部晶片电路相连,为频率管脚,不具备方…时间:2024/08/23 -

; ) 关于芯片外部晶振放置位置的说明

SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT 关于芯片外部晶振放置位置,晶诺威科技说明如下: External Oscillator Pins Many microcontrollers have options for at least two os…时间:2024/08/22

关于芯片外部晶振放置位置的说明

SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT 关于芯片外部晶振放置位置,晶诺威科技说明如下: External Oscillator Pins Many microcontrollers have options for at least two os…时间:2024/08/22 -

; ) 插件晶振密封玻璃珠破裂漏气导致频率错误

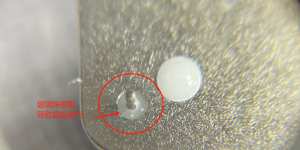

(81.360MHz插件有源晶振PXO-DIP14密封玻璃珠破裂漏气,导致频率错误。) 不良品晶振实测数据: #1:81.353490MHz -80ppm #2:81.356310MHz -45ppm 合格品晶振精度要求: ±30ppm 分析原因: 物理应力导致玻璃珠破裂,晶振漏气。晶振气密…时间:2024/08/21

插件晶振密封玻璃珠破裂漏气导致频率错误

(81.360MHz插件有源晶振PXO-DIP14密封玻璃珠破裂漏气,导致频率错误。) 不良品晶振实测数据: #1:81.353490MHz -80ppm #2:81.356310MHz -45ppm 合格品晶振精度要求: ±30ppm 分析原因: 物理应力导致玻璃珠破裂,晶振漏气。晶振气密…时间:2024/08/21 -

; ) 芯片内部已有RTC时钟为什么还要外挂32.768KHz晶振?

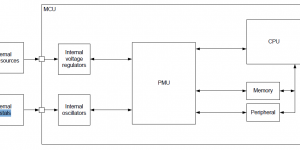

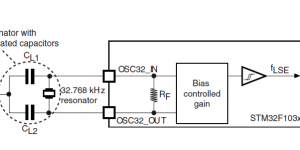

芯片内部已有RTC时钟为什么还要外挂32.768KHz晶振? 答:因为外部晶振提供的时钟信号更稳定,更精准。由RC振荡器提供的RTC内部时钟(internal reference clock source)精度为百分之几,而由石英晶振提供的外部时钟(external reference clock …时间:2024/08/20

芯片内部已有RTC时钟为什么还要外挂32.768KHz晶振?

芯片内部已有RTC时钟为什么还要外挂32.768KHz晶振? 答:因为外部晶振提供的时钟信号更稳定,更精准。由RC振荡器提供的RTC内部时钟(internal reference clock source)精度为百分之几,而由石英晶振提供的外部时钟(external reference clock …时间:2024/08/20 -

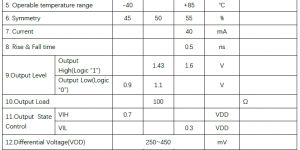

; ) LVDS输出100MHz差分晶振7050 晶振料号D05G100M3LS

晶诺威科技产LVDS输出100MHz差分晶振DO7050规格参数说明如下: 主要参数: PRODUCT TYPE类型: SMD7050 差分晶振 LVDS NOMINAL FREQUENCY标称频率: 100.000000MHz GNW P/N晶振料号: D05G100M3LS 详细参数: 尺寸及引…时间:2024/08/19

LVDS输出100MHz差分晶振7050 晶振料号D05G100M3LS

晶诺威科技产LVDS输出100MHz差分晶振DO7050规格参数说明如下: 主要参数: PRODUCT TYPE类型: SMD7050 差分晶振 LVDS NOMINAL FREQUENCY标称频率: 100.000000MHz GNW P/N晶振料号: D05G100M3LS 详细参数: 尺寸及引…时间:2024/08/19 -

; ) 关于外接电容COG(NPO)贴片电容选型注意事项

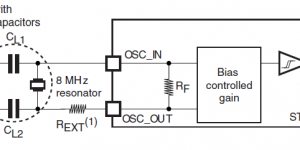

(无源晶振电路中的外接匹配电容CL1和CL2) COG(NPO)贴片电容简述 COG(NPO)贴片电容属于Class 1温度补偿型电容。它的容量稳定,几乎不随温度、电压、时间的变化而变化。尤其适用于高频电子电路。 COG(NPO)贴片电容特性 具有最高的电容量稳定性,在-55℃~125℃工作温度范围…时间:2024/08/18

关于外接电容COG(NPO)贴片电容选型注意事项

(无源晶振电路中的外接匹配电容CL1和CL2) COG(NPO)贴片电容简述 COG(NPO)贴片电容属于Class 1温度补偿型电容。它的容量稳定,几乎不随温度、电压、时间的变化而变化。尤其适用于高频电子电路。 COG(NPO)贴片电容特性 具有最高的电容量稳定性,在-55℃~125℃工作温度范围…时间:2024/08/18 -

; ) 关于晶振电路抗扰性及优化方案

关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…时间:2024/08/17

关于晶振电路抗扰性及优化方案

关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…时间:2024/08/17