关于晶振电路抗扰性及优化方案,晶诺威科技解释如下:

电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。

1、电源噪声

电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运行,进一步加剧失效。

2、电磁干扰

电磁干扰是另一个常见的电路抗扰性问题。电子设备中存在的高频信号源可能引起电磁干扰,从而使晶振的工作受到干扰。

提高电路的抗扰性是解决晶振失效问题的关键,晶诺威科技建议措施如下:

1、加强电源线路的过滤和综合保护,降低电源噪声。可以尝试使用滤波电容、稳压电路等设备来减小电源噪声。

2、设计良好的地线和电源线路布局,降低电磁干扰。可以尝试采用屏蔽罩、隔离层等措施来避免电磁干扰。

3、断开与晶振相关的其他干扰源,如远离高频信号源、电磁辐射源等。

拓展阅读:关于PCB板上晶振如何layout

在很多电路中,系统晶振时钟频率很高,干扰谐波出来的能量也强,谐波除了会从输入与输出两条线导出来外,也会从空间辐射出来,这也导致若PCB中对晶振的布局不够合理,会很容易造成很强的杂散辐射问题,并且一旦产生,很难再通过其他方法来解决,所以在PCB板布局时对晶振和CLK信号线布局非常重要。

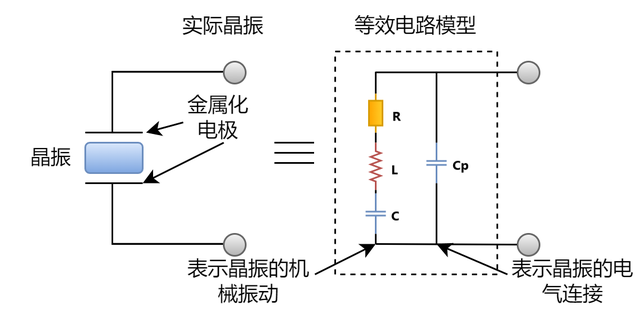

晶振的等效电路

事实上,晶振的作用就像一个串联的RLC电路。

晶振的等效电路显示了一个串联的RLC电路,表示晶振的机械振动,与一个电容并联表示与晶振的电气连接,而晶振振荡器便朝着串联谐振运行工作。

其中,R是ESR等效串联电阻,L和C分别是等效电感和电容,Cp为寄生电容。

晶振在PCB板的设计布局

作为数字电路中的心脏,晶振影响着整个系统的稳定性,系统晶振的选择,决定了数字电路的成败。

由于晶振内部存在石英晶体,受到外部撞击等情况造成晶体断裂,很容易造成晶振不起振,所以通常在电路设计时,要考虑晶振的可靠安装,其位置尽量不要靠近板边、设备外壳等地方。PCB对晶振布局时通常注意以下几点:

1、晶振不能距离板边太近、晶振的外壳必须接地,否则易导致晶振辐射杂讯。

在板卡设计时尤其需要注意这点。外壳接地可以避免晶振向外辐射,同时可以屏蔽外来信号对晶振的干扰。如果一定要布置在PCB边缘,可以在晶振印制线边上再布一根GND线,同时在包地线上间隔一段距离就打过孔,将晶振包围起来。

2、晶振下方不能布信号线,否则易导致信号线耦合晶振谐波杂讯。

保证完全铺地,同时在晶振的300mil范围内不要布线,这样可以防止晶振干扰其他布线、元器件和层的性能。

3、若滤波器件放在晶振下方,且滤波电容与匹配电阻未按照信号流向排布,会使滤波器的滤波效果变差。耦合电容应尽量靠近晶振的电源引脚,按电源流入方向,依据容值从大到小顺序摆放。

4、时钟信号的走线应尽量简短,线宽大一些,在布线长度和远离发热源上寻找平衡。

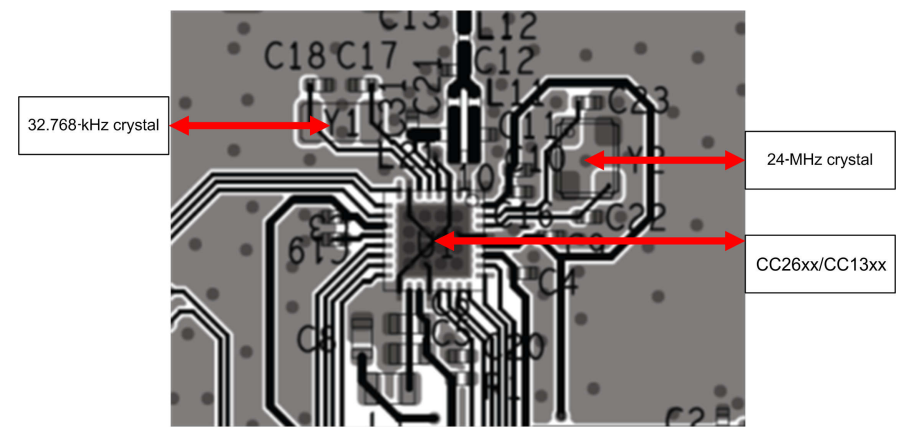

以下图布局为例,晶振的布局方式会相对更优:

1、晶振的滤波电容与匹配电路靠近MCU芯片位置,远离板边。

2、晶振的滤波电容与匹配电阻按照信号流向排布,靠近晶振摆放整齐紧凑。

3、晶振靠近芯片处摆放,到芯片的走线尽量短而直。

在电路系统中,高速时钟信号线优先级最高。时钟线是一个敏感信号,频率越高,要求走线尽量简短,以保证信号的失真度达到最小。