-

; ) 关于电磁干扰对天线接收性能的影响及解决方案

关于电磁干扰对天线接收性能的影响及解决方案,晶诺威科技总结如下: 电磁干扰对天线接收性能的负面影响: 1、电磁干扰会引起天线输入端噪声的增加,导致信号与噪声比(S/N)下降,从而降低接收机的灵敏度。 2、电磁干扰还可能导致天线工作频率范围发生偏移,使得天线无法准确接收特定频段的信号。此外,电磁干扰还…时间:2024/09/04

关于电磁干扰对天线接收性能的影响及解决方案

关于电磁干扰对天线接收性能的影响及解决方案,晶诺威科技总结如下: 电磁干扰对天线接收性能的负面影响: 1、电磁干扰会引起天线输入端噪声的增加,导致信号与噪声比(S/N)下降,从而降低接收机的灵敏度。 2、电磁干扰还可能导致天线工作频率范围发生偏移,使得天线无法准确接收特定频段的信号。此外,电磁干扰还…时间:2024/09/04 -

; ) 关于晶振电路抗扰性及优化方案

关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…时间:2024/08/17

关于晶振电路抗扰性及优化方案

关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…时间:2024/08/17 -

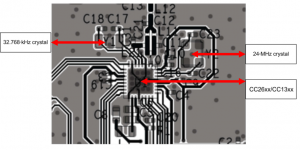

; ) 关于晶振周边电路及晶振匹配电路常见问题及分析

关于晶振周边电路及晶振匹配电路常见问题,晶诺威科技分析如下: 如果晶振经过验证被确认为良品,那么确实需要进一步排查晶振周围的电路以及与电路的匹配问题。以下是详细的排查步骤: 1、检查线路连接 使用万用表:使用万用表的“响铃”功能或电阻档来检查晶振与周围电路的连接是否存在虚焊或短路。虚焊点可能表现为高…时间:2024/06/18

关于晶振周边电路及晶振匹配电路常见问题及分析

关于晶振周边电路及晶振匹配电路常见问题,晶诺威科技分析如下: 如果晶振经过验证被确认为良品,那么确实需要进一步排查晶振周围的电路以及与电路的匹配问题。以下是详细的排查步骤: 1、检查线路连接 使用万用表:使用万用表的“响铃”功能或电阻档来检查晶振与周围电路的连接是否存在虚焊或短路。虚焊点可能表现为高…时间:2024/06/18 -

; ) 如何抑止电磁辐射对时钟信号的干扰?

如果在EMC测试中发现时钟信号的谐波超标严重,在PCB设计中该如何抑止电磁辐射呢? 首先,EMC的三要素为辐射源,传播途径和受害体。而传播途径分为空间辐射传播和电缆传导。所以,要抑制谐波,首先看看它传播的途径。电源去耦(在电源引脚上连接去耦电容)是解决传导方式传播,此外,也要考虑必要的匹配和屏蔽。 …时间:2022/07/09

如何抑止电磁辐射对时钟信号的干扰?

如果在EMC测试中发现时钟信号的谐波超标严重,在PCB设计中该如何抑止电磁辐射呢? 首先,EMC的三要素为辐射源,传播途径和受害体。而传播途径分为空间辐射传播和电缆传导。所以,要抑制谐波,首先看看它传播的途径。电源去耦(在电源引脚上连接去耦电容)是解决传导方式传播,此外,也要考虑必要的匹配和屏蔽。 …时间:2022/07/09 -

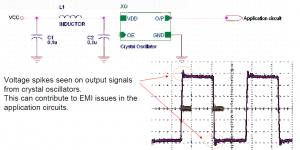

; ) 晶诺威科技产有源晶振EMI消除方案

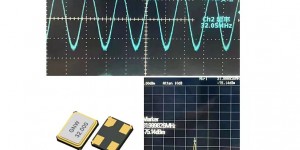

晶诺威科技产有源晶振EMI消除方案解释如下: 1、由下图可见有源晶振输出信号中出现电压尖峰,这可能会给应用电路带来EMI问题。如下图所示: 2、晶诺威科技建议在时钟信号输出端和 GND 之间添加旁路电容( 5-10 pF ),可以使输出波形平滑化,并可显著降低EMI。如下图所示:时间:2022/04/27

晶诺威科技产有源晶振EMI消除方案

晶诺威科技产有源晶振EMI消除方案解释如下: 1、由下图可见有源晶振输出信号中出现电压尖峰,这可能会给应用电路带来EMI问题。如下图所示: 2、晶诺威科技建议在时钟信号输出端和 GND 之间添加旁路电容( 5-10 pF ),可以使输出波形平滑化,并可显著降低EMI。如下图所示:时间:2022/04/27 -

; ) 晶诺威科技产无源贴片晶振EMI消除方案

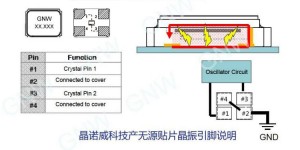

Terminals 2 and 4 on a Genuway crystal unit are connected electrically to the metal cover of the crystal. 晶诺威科技产无源贴片晶振焊盘#2和#4与金属外壳连接。 Genuway recommen…时间:2022/04/27

晶诺威科技产无源贴片晶振EMI消除方案

Terminals 2 and 4 on a Genuway crystal unit are connected electrically to the metal cover of the crystal. 晶诺威科技产无源贴片晶振焊盘#2和#4与金属外壳连接。 Genuway recommen…时间:2022/04/27 -

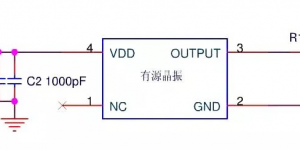

; ) 有源晶振内部电路图,引脚/焊盘说明图及EMC电路接线图

晶诺威科技产无源晶振与有源晶振内部电路图对比如下: 晶诺威科技产有源晶振引脚/焊盘说明 一般情况下,有源晶振有4个脚,有个圆点标记的我们称之为1号脚(PIN1)或脚#1,按逆时针(管脚向下)分别为2、3、4。晶诺威科技产OSC7050有源晶振尺寸及引脚/焊盘说明如下: 脚…时间:2022/04/25

有源晶振内部电路图,引脚/焊盘说明图及EMC电路接线图

晶诺威科技产无源晶振与有源晶振内部电路图对比如下: 晶诺威科技产有源晶振引脚/焊盘说明 一般情况下,有源晶振有4个脚,有个圆点标记的我们称之为1号脚(PIN1)或脚#1,按逆时针(管脚向下)分别为2、3、4。晶诺威科技产OSC7050有源晶振尺寸及引脚/焊盘说明如下: 脚…时间:2022/04/25 -

; ) 降低晶振振荡电路中EMI的解决方案是什么?

Electromagnetic interference (or EMI, also called radio frequency interference or RFI) is a (usually undesirable) disturbance that affects an electric…时间:2022/04/11

降低晶振振荡电路中EMI的解决方案是什么?

Electromagnetic interference (or EMI, also called radio frequency interference or RFI) is a (usually undesirable) disturbance that affects an electric…时间:2022/04/11 -

; ) 如何解决有源晶振对电源的干扰问题?

在有源晶振的电路应用中,我们该如何尽量避免其对电源的干扰呢? 晶诺威科技建议PCB设计如下: 1、晶振外壳接地设计,目的是防止晶振信号的向外辐射,同时屏蔽外来杂波干扰。 2、晶振所在层铺地设计,目的是防止晶振信号干扰其它层。 3、建议晶振下面不要布线,其周围5毫米范围内不要设计布线及安置其它电子元件…时间:2020/12/24

如何解决有源晶振对电源的干扰问题?

在有源晶振的电路应用中,我们该如何尽量避免其对电源的干扰呢? 晶诺威科技建议PCB设计如下: 1、晶振外壳接地设计,目的是防止晶振信号的向外辐射,同时屏蔽外来杂波干扰。 2、晶振所在层铺地设计,目的是防止晶振信号干扰其它层。 3、建议晶振下面不要布线,其周围5毫米范围内不要设计布线及安置其它电子元件…时间:2020/12/24 -

; ) 晶振与时钟信号的关系

时钟信号在电路板中,起到重要的类似“信号灯”的作用。若时钟信号受到足够干扰,可能电路板系统紊乱,表现形式为不开机或开机不良。因此,我们建议在设计时钟信号走线时,请注意以下内容: 晶振时钟信号走线的方式取决于你所采用的分配方案:比如是公共时钟同步还是源时钟同步,要不要加时钟分配器件,加几级驱动等。 实…时间:2020/10/14

晶振与时钟信号的关系

时钟信号在电路板中,起到重要的类似“信号灯”的作用。若时钟信号受到足够干扰,可能电路板系统紊乱,表现形式为不开机或开机不良。因此,我们建议在设计时钟信号走线时,请注意以下内容: 晶振时钟信号走线的方式取决于你所采用的分配方案:比如是公共时钟同步还是源时钟同步,要不要加时钟分配器件,加几级驱动等。 实…时间:2020/10/14