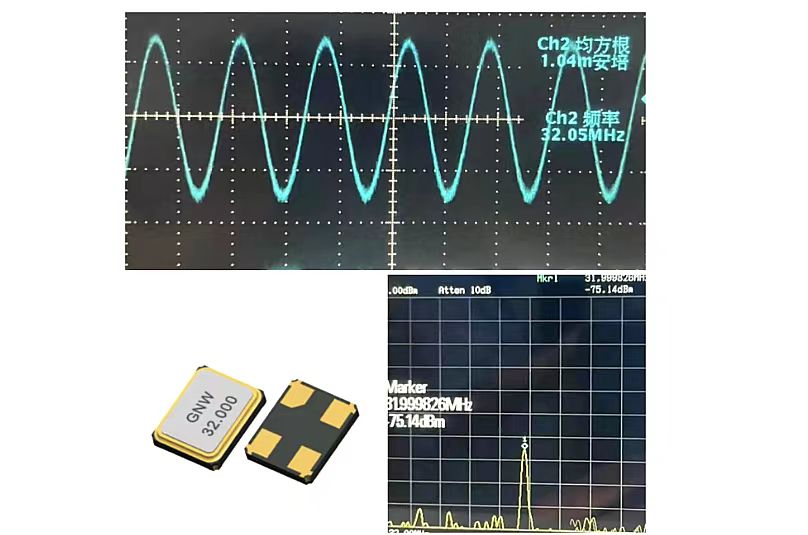

时钟信号在电路板中,起到重要的类似“信号灯”的作用。若时钟信号受到足够干扰,可能电路板系统紊乱,表现形式为不开机或开机不良。因此,我们建议在设计时钟信号走线时,请注意以下内容:

晶振时钟信号走线的方式取决于你所采用的分配方案:比如是公共时钟同步还是源时钟同步,要不要加时钟分配器件,加几级驱动等。

实际走线长短根据分配方案和拓扑结构具体计算(当然,信号线路越短越好),时钟分配器件下要铺铜,未用引脚用1K电阻下拉到地。多级驱动要加PLL补偿(补偿值的大小需要计算)。

建议晶振输出的时钟信号不要分叉。若实在没有办法而必须要分叉的话,最多分两路(特指低速,高速必须点对点),其他情况必须加时钟驱动。时钟驱动最多带两个负载。提醒一下,时钟信号分叉后相位存在跑偏隐患。

关于晶振时钟信号线路布局的建议:

1、时钟电路周围走低速低压信号电路

2、远离电源

3、在同层走线

4、保证阻抗连续

5、尽量走在少受杂散信号干扰的内层

6、晶振不要靠近电路板边缘

7、走等长线的部分周围要留出足够的空间(注意3W规则,100M以上时钟线必须拉圆弧线)。点对点、菊花链结构最常用。

8、晶振下最好不要走线,尤其是高速信号线。

9、注意大电容焊盘的特殊处理,要求保证电流供电能力。

拓展阅读:为什么把晶振设计在IC旁?

在IC集成电路布局和设计中,将晶振(晶体振荡器)放置在靠近IC(集成电路)的位置是一种优化的做法,晶诺威科技为您归纳了以下八点:

1、信号稳定性

晶振是产生稳定时钟信号的关键组件,将晶振放在IC附近可以最大程度地减小时钟信号传输的损耗和干扰。信号的传输距离越短,时钟信号的稳定性就越高。

这是因为信号的传输过程中可能会受到各种因素的干扰,如电磁干扰、电阻、电容等,这些因素都可能导致信号的失真或衰减。因此,将晶振放在IC附近可以确保时钟信号的清晰度和准确性,从而提高整个系统的性能。

2、传输效率

当时钟信号经过较长的传输线路后会产生微小的传输延迟。而微控制器通常具有非常高的时钟频率,任何微小的延迟都会对系统性能产生显著的影响。将晶振放置在IC附近可以缩短时钟信号的传输距离,从而减少传输延迟。这有助于提高系统的响应速度和整体性能,特别是在需要高速数据传输和处理的应用中。

3、抗干扰能力

晶振产生的时钟信号具有一定的电磁辐射,如果与其他电子组件放置过远,可能会产生电磁干扰(EMI)。将晶振放置在IC附近可以减少这种干扰,提高系统的电磁兼容性。可以最大限度地减小外界干扰对时钟信号的影响,确保系统在复杂电磁环境中稳定运行,减少故障和错误的发生。

4、电源管理

将晶振放置在IC附近还有助于电源管理。晶振的工作需要稳定的电源供应,将其放置在IC附近可以确保电源线路连接更为直接和稳定,减少电源波动对晶振工作的影响,从而保持晶振的稳定运行。

5、热管理

晶振在工作时会产生一定的热量,特别是在高频或高温环境下。因此,将晶振放置在集成电路附近时,需要考虑到热管理的因素。通常,设计师会选择在集成电路的散热片或散热孔附近放置晶振,以便有效地将热量散发出去,防止热量积累导致性能下降或设备损坏。

6、布局优化

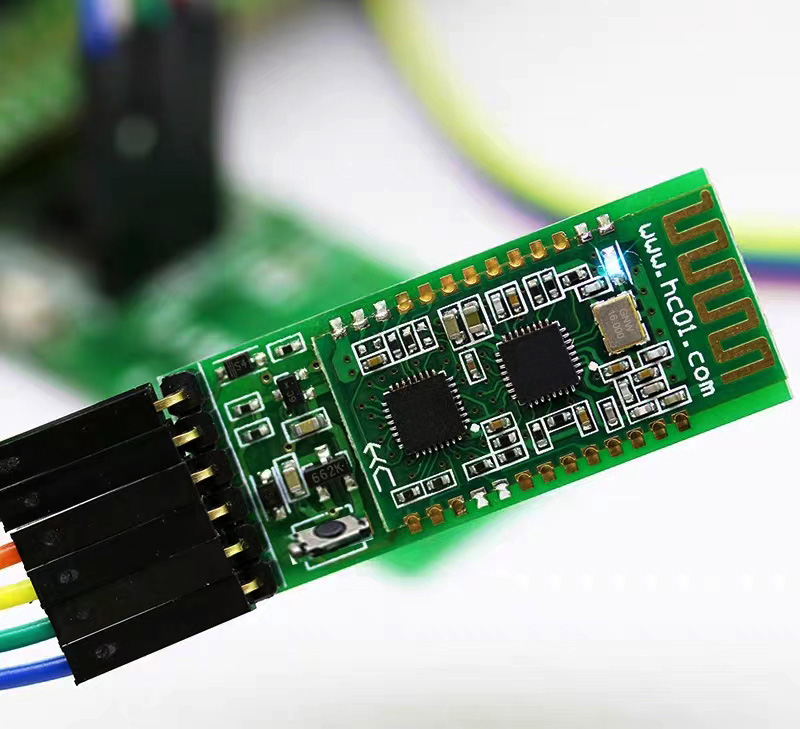

在电子设备的布局设计中,通常需要考虑组件之间的空间关系和相互影响。晶振的大小和形状可能会限制其在电路板上的放置位置。在满足信号质量、传输效率和电磁兼容性的同时,将晶振放在IC附近可以实现布局的优化,提高整体电路板的紧凑性和可靠性。

7、兼容性考虑

某些特定的IC可能需要与特定类型的晶振配合使用,以确保最佳的性能和兼容性。将晶振放置在IC附近可以确保它们之间的连接更加直接和可靠,减少因线路过长或信号干扰而引起的兼容性问题。

8、成本考虑

虽然将晶振放置在集成电路附近可能会带来一些优势,但这也可能增加设计的复杂性和成本。例如,可能需要使用更高级的布线技术或更昂贵的材料来确保信号质量和电磁兼容性。因此,在设计中需要综合考虑这些因素,以找到最佳的平衡点。

综上所述,将晶振放在IC附近是出于对信号稳定性、传输延迟、抗干扰能力、电源管理、布局优化和兼容性等多方面的考虑。这种布局设计有助于确保电子设备能够高效、稳定地运行,提高系统的性能和可靠性,并确保数字电路能够正常工作。