-

; ) 关于电磁干扰对天线接收性能的影响及解决方案

关于电磁干扰对天线接收性能的影响及解决方案,晶诺威科技总结如下: 电磁干扰对天线接收性能的负面影响: 1、电磁干扰会引起天线输入端噪声的增加,导致信号与噪声比(S/N)下降,从而降低接收机的灵敏度。 2、电磁干扰还可能导致天线工作频率范围发生偏移,使得天线无法准确接收特定频段的信号。此外,电磁干扰还…时间:2024/09/04

关于电磁干扰对天线接收性能的影响及解决方案

关于电磁干扰对天线接收性能的影响及解决方案,晶诺威科技总结如下: 电磁干扰对天线接收性能的负面影响: 1、电磁干扰会引起天线输入端噪声的增加,导致信号与噪声比(S/N)下降,从而降低接收机的灵敏度。 2、电磁干扰还可能导致天线工作频率范围发生偏移,使得天线无法准确接收特定频段的信号。此外,电磁干扰还…时间:2024/09/04 -

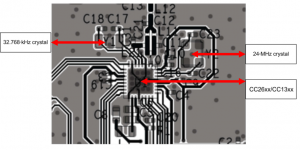

; ) 射频天线会干扰到电路板晶振吗?

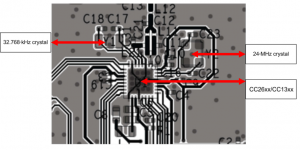

射频天线会干扰到电路板晶振吗? 答:是的,如果天线距离晶振太近,天线和晶振都会相互干扰。 晶诺威科技解释如下: 射频天线在工作时会产生较强的电磁辐射,这些辐射可能耦合到晶振或其走线上,影响晶振的正常工作。 射频天线可能会干扰电路板上的晶振,导致频率偏差、信号抖动或系统崩溃。通过优化布局、增加屏蔽、改…时间:2024/09/01

射频天线会干扰到电路板晶振吗?

射频天线会干扰到电路板晶振吗? 答:是的,如果天线距离晶振太近,天线和晶振都会相互干扰。 晶诺威科技解释如下: 射频天线在工作时会产生较强的电磁辐射,这些辐射可能耦合到晶振或其走线上,影响晶振的正常工作。 射频天线可能会干扰电路板上的晶振,导致频率偏差、信号抖动或系统崩溃。通过优化布局、增加屏蔽、改…时间:2024/09/01 -

; ) 关于晶振电路抗扰性及优化方案

关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…时间:2024/08/17

关于晶振电路抗扰性及优化方案

关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…时间:2024/08/17 -

; ) 电子设计中的EMI和EMC有什么区别?

(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele…时间:2024/06/10

电子设计中的EMI和EMC有什么区别?

(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele…时间:2024/06/10 -

; ) 如何最大程度减少晶振电路中的串扰信号及EMI?

如何最大程度减少晶振电路中的串扰信号及EMI?晶诺威科技解答如下: ( Low-Frequency Oscillator with Quartz Crystal 32.768KHz) As is shown above,The oscillator circuit consists of an in…时间:2024/06/08

如何最大程度减少晶振电路中的串扰信号及EMI?

如何最大程度减少晶振电路中的串扰信号及EMI?晶诺威科技解答如下: ( Low-Frequency Oscillator with Quartz Crystal 32.768KHz) As is shown above,The oscillator circuit consists of an in…时间:2024/06/08 -

; ) 无线门铃27.13827MHz负载电容15pF晶振SMD3225-4p规格参数说明

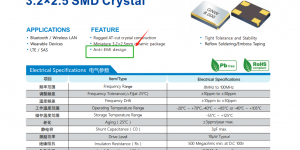

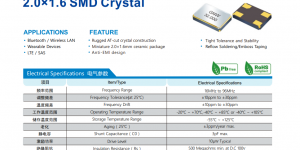

(无线门铃) 晶诺威科技产SMD3225-4p晶振27.13827MHz主要参数如下: 标称频率 Nominal Frequency:27.13827MHz 晶体切型Cutting Mode:AT Cut 封装类型 Holder Type:无源贴片晶振 SMD 3.2mm*2.5mm 焊盘数量Pad…时间:2024/05/17

无线门铃27.13827MHz负载电容15pF晶振SMD3225-4p规格参数说明

(无线门铃) 晶诺威科技产SMD3225-4p晶振27.13827MHz主要参数如下: 标称频率 Nominal Frequency:27.13827MHz 晶体切型Cutting Mode:AT Cut 封装类型 Holder Type:无源贴片晶振 SMD 3.2mm*2.5mm 焊盘数量Pad…时间:2024/05/17 -

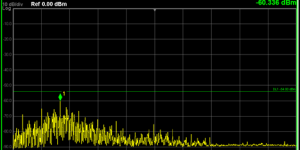

; ) 晶振会产生电磁波干扰吗?

晶振会产生电磁波干扰吗? 答:会的。 晶诺威科技解释如下: 传统排除晶振电磁波干扰的方式:在回路中加入磁珠、滤波器、接地回路、以及金属屏蔽罩。作为晶振厂家,晶诺威科技也在优化晶振本身材质及电路设计,尽最大可能降低晶振对外界的干扰,同时,也增强了自身抗(来自外界的)干扰能力。 在有源晶振方面,则增加了…时间:2024/05/12

晶振会产生电磁波干扰吗?

晶振会产生电磁波干扰吗? 答:会的。 晶诺威科技解释如下: 传统排除晶振电磁波干扰的方式:在回路中加入磁珠、滤波器、接地回路、以及金属屏蔽罩。作为晶振厂家,晶诺威科技也在优化晶振本身材质及电路设计,尽最大可能降低晶振对外界的干扰,同时,也增强了自身抗(来自外界的)干扰能力。 在有源晶振方面,则增加了…时间:2024/05/12 -

; ) 为什么在有些晶振应用中会出现噪声干扰?

为什么在有些晶振应用中会出现噪声干扰? 答:噪声干扰可能是由于电源干扰、电磁干扰(EMI)等因素引起的。为了解决这个问题,可以尝试调整电路设计以减少干扰源、使用滤波器或屏蔽措施等。同时,需要注意电路板的布局和布线对噪声干扰的影响。 拓展阅读:噪声 (Noise)、电磁干扰(EMI)与电磁兼容性(EM…时间:2024/03/22

为什么在有些晶振应用中会出现噪声干扰?

为什么在有些晶振应用中会出现噪声干扰? 答:噪声干扰可能是由于电源干扰、电磁干扰(EMI)等因素引起的。为了解决这个问题,可以尝试调整电路设计以减少干扰源、使用滤波器或屏蔽措施等。同时,需要注意电路板的布局和布线对噪声干扰的影响。 拓展阅读:噪声 (Noise)、电磁干扰(EMI)与电磁兼容性(EM…时间:2024/03/22 -

; ) 关于RF设备中晶振单独接地(GND)与共地问题

关于RF设备中晶振单独接地(GND)与共地问题,晶诺威科技解释如下: 举例,某款RF设备接地说明如下: The ground plane of the RF application board is separated into four independent fragments: the ana…时间:2024/03/15

关于RF设备中晶振单独接地(GND)与共地问题

关于RF设备中晶振单独接地(GND)与共地问题,晶诺威科技解释如下: 举例,某款RF设备接地说明如下: The ground plane of the RF application board is separated into four independent fragments: the ana…时间:2024/03/15

; )