-

; ) 内置负载电容还需要外接电容吗?

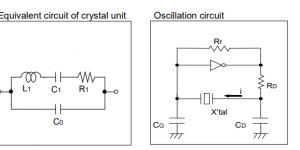

内置负载电容还需要外接电容吗? 答:通常所说的内置负载电容指的是晶振的电气参数---负载电容(CL)。 一般情况下,在无源晶振实际电路应用中需要外接匹配电容。如下图所示: 晶诺威科技产无源晶振SMD3225-4PIN规格参数如下: 外接电容的作用主要是修正无源晶振的实际输出频率的精度。 这里需要特别…时间:2023/05/10

内置负载电容还需要外接电容吗?

内置负载电容还需要外接电容吗? 答:通常所说的内置负载电容指的是晶振的电气参数---负载电容(CL)。 一般情况下,在无源晶振实际电路应用中需要外接匹配电容。如下图所示: 晶诺威科技产无源晶振SMD3225-4PIN规格参数如下: 外接电容的作用主要是修正无源晶振的实际输出频率的精度。 这里需要特别…时间:2023/05/10 -

; ) 无源晶振容易受到杂散讯号干扰吗?

无源晶振容易受到杂散讯号干扰吗? 答:是的,无源晶振(晶体谐振器)的振荡电路非常容易受到周边信号干扰,造成频率不稳定。 建议晶振远离信号辐射源,如电源、天线、蜂鸣器、电机、风扇及板边等。 如果对晶振信号精度及稳定度有着高要求,也就意味着对晶振有抗干扰性有要求,建议选择三脚或四脚高精度无源晶振,而不是…时间:2023/04/21

无源晶振容易受到杂散讯号干扰吗?

无源晶振容易受到杂散讯号干扰吗? 答:是的,无源晶振(晶体谐振器)的振荡电路非常容易受到周边信号干扰,造成频率不稳定。 建议晶振远离信号辐射源,如电源、天线、蜂鸣器、电机、风扇及板边等。 如果对晶振信号精度及稳定度有着高要求,也就意味着对晶振有抗干扰性有要求,建议选择三脚或四脚高精度无源晶振,而不是…时间:2023/04/21 -

; ) 无源晶振外接谐振电容调整方法

无源晶振外接谐振电容调整方法说明如下: 如果电路中心频率正偏时,可以下调晶振外接谐振电容的值,如果电路中心频率负偏时,可以上调晶振外接谐振电容值。一般情况下,两颗外接谐振电容值微调范围分别为:0~33PF。 注: 1、以上调节方法基于晶振本身中心频率精度合格。 2、以上调节方法仅限于对晶振工作中发生…时间:2023/03/28

无源晶振外接谐振电容调整方法

无源晶振外接谐振电容调整方法说明如下: 如果电路中心频率正偏时,可以下调晶振外接谐振电容的值,如果电路中心频率负偏时,可以上调晶振外接谐振电容值。一般情况下,两颗外接谐振电容值微调范围分别为:0~33PF。 注: 1、以上调节方法基于晶振本身中心频率精度合格。 2、以上调节方法仅限于对晶振工作中发生…时间:2023/03/28 -

; ) 81.360MHz无源插件晶振49U规格参数说明

关于晶诺威科技产81.360MHz无源插件晶振49U规格参数说明如下: (无源插件晶振49U电路应用) 晶诺威科技产81.360MHz无源插件晶振 49U主要电气参数: Nominal Frequency 标称频率: 81.360MHz Oscillation Mode振荡模式:3rd Overto…时间:2023/03/15

81.360MHz无源插件晶振49U规格参数说明

关于晶诺威科技产81.360MHz无源插件晶振49U规格参数说明如下: (无源插件晶振49U电路应用) 晶诺威科技产81.360MHz无源插件晶振 49U主要电气参数: Nominal Frequency 标称频率: 81.360MHz Oscillation Mode振荡模式:3rd Overto…时间:2023/03/15 -

; ) 晶振的作用及晶振电路PCB设计

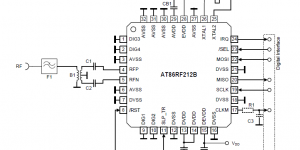

关于晶振的作用及晶振电路PCB设计,晶诺威科技介绍如下: 晶振的作用 一个数字电路就像一个城市的交通,晶振的作用就是十字路口的信号灯。数字电路又像生命体,它的运行就像人身体里的血液流通,它不是由单一的某个器件或器件单元构成,而是由多个器件及程序彼此配合、协调,共同完成良性的运转。晶振电路由晶振和相关…时间:2023/03/14

晶振的作用及晶振电路PCB设计

关于晶振的作用及晶振电路PCB设计,晶诺威科技介绍如下: 晶振的作用 一个数字电路就像一个城市的交通,晶振的作用就是十字路口的信号灯。数字电路又像生命体,它的运行就像人身体里的血液流通,它不是由单一的某个器件或器件单元构成,而是由多个器件及程序彼此配合、协调,共同完成良性的运转。晶振电路由晶振和相关…时间:2023/03/14 -

; ) 无源晶振正弦波输出正常/无波形/幅值低/畸变

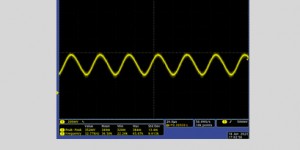

关于无源晶振波形输出正常与异常,对比如下: 无源晶振波形正常输出(无源晶振起振正常),如下图所示: 无源晶振波形输出异常(无源晶振起振不正常),如下图所示: 无源晶振波形输出异常原因很多,主要分三个方面: 1、晶振型号选错 包括:晶振负载选错、晶振外接电容选错、晶振精度选错、工作温度选错等。 2、晶…时间:2023/02/11

无源晶振正弦波输出正常/无波形/幅值低/畸变

关于无源晶振波形输出正常与异常,对比如下: 无源晶振波形正常输出(无源晶振起振正常),如下图所示: 无源晶振波形输出异常(无源晶振起振不正常),如下图所示: 无源晶振波形输出异常原因很多,主要分三个方面: 1、晶振型号选错 包括:晶振负载选错、晶振外接电容选错、晶振精度选错、工作温度选错等。 2、晶…时间:2023/02/11 -

; ) 不合理的PCB设计也可能造成晶振不起振

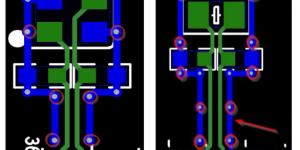

不合理的PCB设计也可能造成晶振不起振,归纳五点建议如下: 1、若无源晶振距离板边太近,则易导致晶振辐射杂讯或超声波焊接破坏,建议离PCB板边10mm以上。晶振位置不合理设计,如下面两图所示: (图一) (图二) 2、无源晶振电路尽可能地靠近芯片的时钟管脚放…时间:2023/01/03

不合理的PCB设计也可能造成晶振不起振

不合理的PCB设计也可能造成晶振不起振,归纳五点建议如下: 1、若无源晶振距离板边太近,则易导致晶振辐射杂讯或超声波焊接破坏,建议离PCB板边10mm以上。晶振位置不合理设计,如下面两图所示: (图一) (图二) 2、无源晶振电路尽可能地靠近芯片的时钟管脚放…时间:2023/01/03 -

; ) 关于晶体谐振器电路应用三个常见误区

关于晶体谐振器电路应用三个常见误区,晶诺威科技为您整理如下: Drive level 驱动电平 Applying excessive drive level to the crystal units may cause deterioration of characteristics or dama…时间:2022/10/15

关于晶体谐振器电路应用三个常见误区

关于晶体谐振器电路应用三个常见误区,晶诺威科技为您整理如下: Drive level 驱动电平 Applying excessive drive level to the crystal units may cause deterioration of characteristics or dama…时间:2022/10/15 -

; ) 为何晶振的时钟电路要优先设计?

我们都知道,构建一套完整且正确的数字电路需要做出很多复杂的步骤。为了实现某些特定的功能及性能,我们除了选取合适的电子元件以外,还要考虑如何以最佳的方案把它们构建在一起。那么,何时是一个最佳的时间来解决时钟信号的问题呢?换句话说,晶体谐振器或晶体振荡器是优先考虑还是放在最后再考虑呢? 晶诺威科技认为在…时间:2022/10/09

为何晶振的时钟电路要优先设计?

我们都知道,构建一套完整且正确的数字电路需要做出很多复杂的步骤。为了实现某些特定的功能及性能,我们除了选取合适的电子元件以外,还要考虑如何以最佳的方案把它们构建在一起。那么,何时是一个最佳的时间来解决时钟信号的问题呢?换句话说,晶体谐振器或晶体振荡器是优先考虑还是放在最后再考虑呢? 晶诺威科技认为在…时间:2022/10/09 -

; ) 无源晶振,有源晶振与石英晶体的关系

石英晶体谐振器、石英晶体振荡器、石英晶体滤波器均为石英晶体元器件。我们常说的无源晶振其全称是石英晶体谐振器,而有源晶振则是指石英晶体振荡器,它们都是石英晶体元器件中的一种。 石英晶体是一种压电晶体。压电晶体当受特定方向挤压或拉伸时,它的两端就会产生不同的电荷。根据效应情况不同,分为正压电效应与逆压电…时间:2022/08/07

无源晶振,有源晶振与石英晶体的关系

石英晶体谐振器、石英晶体振荡器、石英晶体滤波器均为石英晶体元器件。我们常说的无源晶振其全称是石英晶体谐振器,而有源晶振则是指石英晶体振荡器,它们都是石英晶体元器件中的一种。 石英晶体是一种压电晶体。压电晶体当受特定方向挤压或拉伸时,它的两端就会产生不同的电荷。根据效应情况不同,分为正压电效应与逆压电…时间:2022/08/07