-

; ) 为什么在有些晶振应用中会出现噪声干扰?

为什么在有些晶振应用中会出现噪声干扰? 答:噪声干扰可能是由于电源干扰、电磁干扰(EMI)等因素引起的。为了解决这个问题,可以尝试调整电路设计以减少干扰源、使用滤波器或屏蔽措施等。同时,需要注意电路板的布局和布线对噪声干扰的影响。 拓展阅读:噪声 (Noise)、电磁干扰(EMI)与电磁兼容性(EM…时间:2024/03/22

为什么在有些晶振应用中会出现噪声干扰?

为什么在有些晶振应用中会出现噪声干扰? 答:噪声干扰可能是由于电源干扰、电磁干扰(EMI)等因素引起的。为了解决这个问题,可以尝试调整电路设计以减少干扰源、使用滤波器或屏蔽措施等。同时,需要注意电路板的布局和布线对噪声干扰的影响。 拓展阅读:噪声 (Noise)、电磁干扰(EMI)与电磁兼容性(EM…时间:2024/03/22 -

; ) 关于晶振应用常见问题及实际案例分析

关于晶振应用常见问题及实际案例,晶诺威科技总结并分析如下: 晶振型号选择不当 案例:某设计团队在开发一款高性能通信设备时,为节省成本,选择了无源晶振作为时钟源。然而,在测试过程中发现,设备的信号质量较差,通信性能无法达到预期。 解决方案:分析问题原因,发现由于无源晶振频率稳定性较差,导致通信性能不佳…时间:2023/08/23

关于晶振应用常见问题及实际案例分析

关于晶振应用常见问题及实际案例,晶诺威科技总结并分析如下: 晶振型号选择不当 案例:某设计团队在开发一款高性能通信设备时,为节省成本,选择了无源晶振作为时钟源。然而,在测试过程中发现,设备的信号质量较差,通信性能无法达到预期。 解决方案:分析问题原因,发现由于无源晶振频率稳定性较差,导致通信性能不佳…时间:2023/08/23 -

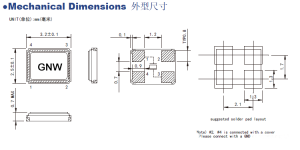

; ) 无源晶振的第1脚和第3脚的接法

(4脚无源晶振SMD3225尺寸及脚位说明) 一般情况下,4脚无源晶振的第1脚和第3脚的接法如下: 无源晶振的第1脚和第3脚其实没有方向性,不用担忧接反。 具体操作: 若脚1接OSC-IN(频率输入),则脚3接OSC-OUT(频率输出) 若脚3接OSC-OUT(频率输出),则脚1接OSC-IN(频率…时间:2022/11/14

无源晶振的第1脚和第3脚的接法

(4脚无源晶振SMD3225尺寸及脚位说明) 一般情况下,4脚无源晶振的第1脚和第3脚的接法如下: 无源晶振的第1脚和第3脚其实没有方向性,不用担忧接反。 具体操作: 若脚1接OSC-IN(频率输入),则脚3接OSC-OUT(频率输出) 若脚3接OSC-OUT(频率输出),则脚1接OSC-IN(频率…时间:2022/11/14 -

; ) PCBA如何避免高频信号干扰?

PCBA如何避免高频信号干扰? 在PCBA上,避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。 为避免高频干扰,晶诺威科技建议方法如下: 1、拉大高速信号和模拟信号之间的距离 2、增加groundguard/shunttraces在模拟信号旁边 3、注意…时间:2022/07/08

PCBA如何避免高频信号干扰?

PCBA如何避免高频信号干扰? 在PCBA上,避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。 为避免高频干扰,晶诺威科技建议方法如下: 1、拉大高速信号和模拟信号之间的距离 2、增加groundguard/shunttraces在模拟信号旁边 3、注意…时间:2022/07/08 -

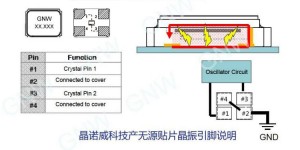

; ) 晶诺威科技产无源贴片晶振EMI消除方案

Terminals 2 and 4 on a Genuway crystal unit are connected electrically to the metal cover of the crystal. 晶诺威科技产无源贴片晶振焊盘#2和#4与金属外壳连接。 Genuway recommen…时间:2022/04/27

晶诺威科技产无源贴片晶振EMI消除方案

Terminals 2 and 4 on a Genuway crystal unit are connected electrically to the metal cover of the crystal. 晶诺威科技产无源贴片晶振焊盘#2和#4与金属外壳连接。 Genuway recommen…时间:2022/04/27 -

; ) 降低晶振振荡电路中EMI的解决方案是什么?

Electromagnetic interference (or EMI, also called radio frequency interference or RFI) is a (usually undesirable) disturbance that affects an electric…时间:2022/04/11

降低晶振振荡电路中EMI的解决方案是什么?

Electromagnetic interference (or EMI, also called radio frequency interference or RFI) is a (usually undesirable) disturbance that affects an electric…时间:2022/04/11 -

; ) 如何减少寄生电容对晶振造成的辐射干扰?

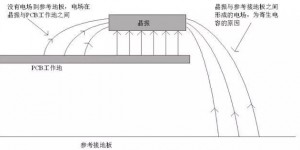

若晶振正好布线于电路板边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶振与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越…时间:2021/06/15

如何减少寄生电容对晶振造成的辐射干扰?

若晶振正好布线于电路板边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶振与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越…时间:2021/06/15 -

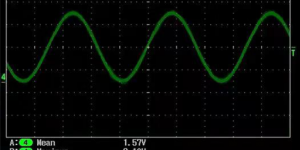

; ) 如何减少辐射对时钟信号的干扰?

晶振在电路板中起到提供时钟信号的关键作用。我们在布线时应该优先设计晶振的位置,以规避时钟受周围信号干扰而导致电路板上电不良之隐患。 1、有正弦波输出的贴片晶振,输出负载为10k;如果10k的负载能力不够,必须加缓冲电路,使PLL的参考与单片机的时钟相隔离; 2、晶振输出到PLL的信号线不能长,否则再…时间:2020/10/13

如何减少辐射对时钟信号的干扰?

晶振在电路板中起到提供时钟信号的关键作用。我们在布线时应该优先设计晶振的位置,以规避时钟受周围信号干扰而导致电路板上电不良之隐患。 1、有正弦波输出的贴片晶振,输出负载为10k;如果10k的负载能力不够,必须加缓冲电路,使PLL的参考与单片机的时钟相隔离; 2、晶振输出到PLL的信号线不能长,否则再…时间:2020/10/13 -

; ) EMC测试项目及电磁波对晶振的影响

EMC全称Electro Magnetic Compatibility,指设备或系统在其电磁环境中能正常工作,且不对该环境中任何事物构成不能承受的电磁骚扰的能力。EMC是评价电子产品质量的一个重要指标。 从广义上讲,EMC测试的具体项目包括以下两个大项: (1)EMI(Electro-Magneti…时间:2020/09/17

EMC测试项目及电磁波对晶振的影响

EMC全称Electro Magnetic Compatibility,指设备或系统在其电磁环境中能正常工作,且不对该环境中任何事物构成不能承受的电磁骚扰的能力。EMC是评价电子产品质量的一个重要指标。 从广义上讲,EMC测试的具体项目包括以下两个大项: (1)EMI(Electro-Magneti…时间:2020/09/17 -

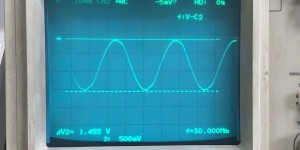

; ) 晶振频率受干扰的不良现象和解决方案

当系统启动失败或显示器画面受干扰时,该类问题可能是因为晶振所输出频率遭受到周边其它信号干扰所致。 晶诺威科技建议解决方案如下: 1、在晶振频率受干扰状态,使用频率计数器检测实时晶振的频率是否正常。 2、如果晶振频率受干扰自电源的交流电信号,请检查电源是否接地及信号处于接地浮空状态。若没…时间:2020/07/18

晶振频率受干扰的不良现象和解决方案

当系统启动失败或显示器画面受干扰时,该类问题可能是因为晶振所输出频率遭受到周边其它信号干扰所致。 晶诺威科技建议解决方案如下: 1、在晶振频率受干扰状态,使用频率计数器检测实时晶振的频率是否正常。 2、如果晶振频率受干扰自电源的交流电信号,请检查电源是否接地及信号处于接地浮空状态。若没…时间:2020/07/18