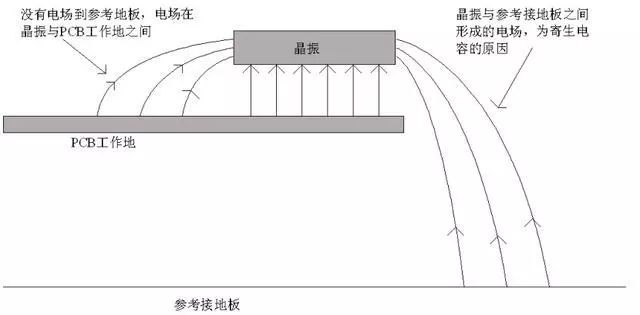

若晶振正好布线于电路板边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶振与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越大,对晶振造成的辐射干扰就会越强。

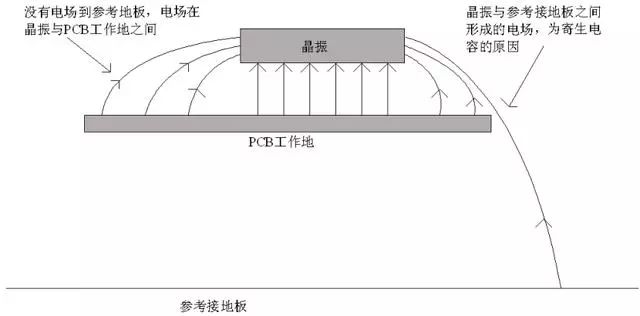

晶振在电路板边缘与在电路板中间时电场分布如下:

(图一)

(图二)

从以上两张图示可以看出,当晶振由图一位置移到图二位置时,即远离电路板边缘时,由于电路板中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地之间,即在电路板内部,分布到参考接地板的电场大大减小,同时降低了寄生电容对晶振的辐射干扰。

结论

当晶振设计在电路板边缘时,建议将晶振内移,使其离电路板边缘至少1cm以上,并在电路板表层距离晶振1cm的范围内敷铜,同时把表层的铜通过过孔与电路板地平面相连。如果处于某种原因不得不布置晶振于电路板边缘,建议在印制线边上增加一根工作地线,同时增加过孔将此工作地线与工作地平面相连,借此尽可能降低寄生电容对晶振的辐射干扰。最后提醒针对晶振布线时,请尽可能远离电源组件。