晶振PCB正确布线的重要性

晶振PCB正确布线直接决定着电路板是否上电后正常及稳定工作,因此其重要性千万不可忽略。

如何避免晶振受干扰?

为了避免晶振受到PCB边缘的干扰,通常可以采取以下措施:将晶振放置在离PCB边缘一定距离的位置,以减少外界干扰的影响;在晶振周围设置合适的屏蔽罩,以减少外界电磁辐射的影响;考虑机械固定的问题,避免晶振受到机械振动的影响;合理规划晶振的布局,避免与其他元器件产生电磁干扰;合理规划散热措施,以减少温度变化对晶振的影响。

在晶振布线设计中应该注意的原则性事项:

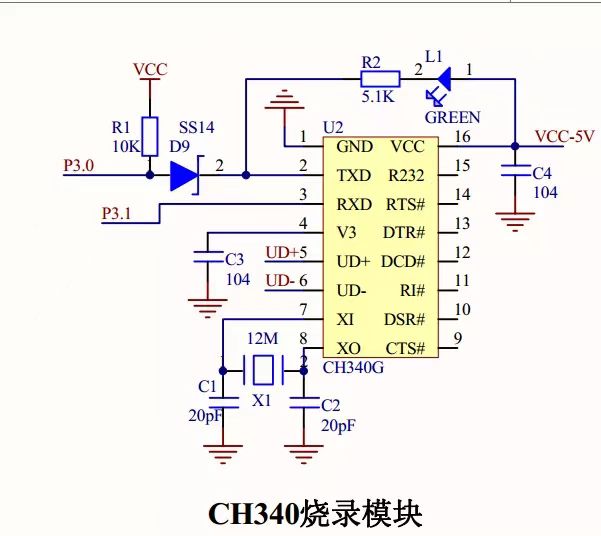

1、X1和X2晶振引脚均为高阻引脚,必须小心处理。需确保晶体与X1,X2引脚之间的连线距离最短,必须小于5mm。

2、确保VDD引脚具有良好的退藕性。(VDD与地之间连接一个0.1uF电容)

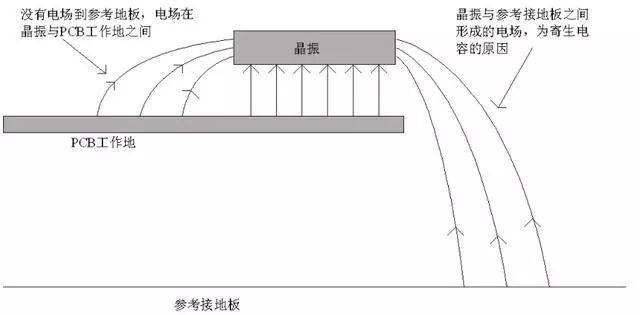

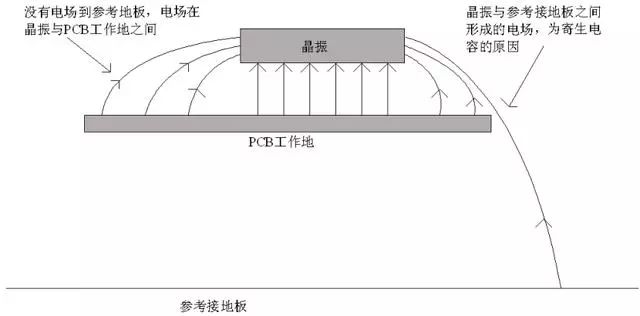

3、即使信号位于板内层,也不能允许信号线靠近X1和X2引脚。在晶体引脚周围使用接地保护环。在内部或板反面使用接地保护敷铜。

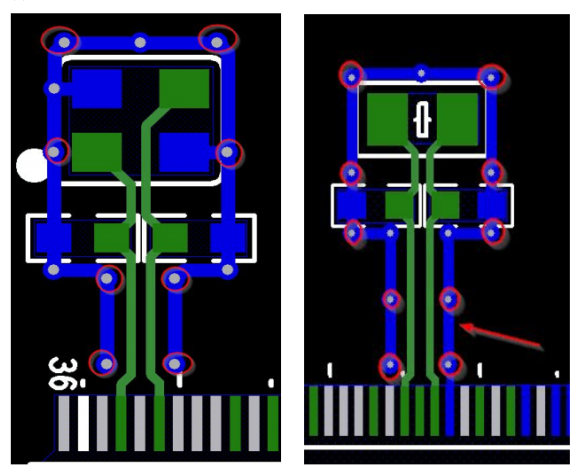

1、晶振电路尽量靠近芯片端,并且与其输出时钟相关的时钟线走线等长,等阻抗。

2、走线尽量短,与其他信号需20mil间距,最好使用接地与其他信号隔离。

3、晶振底下尽量不要走线。如果实在要走线的话,不能走线进晶振pin脚周围50mil之内。尤其要避免高速讯号。

注:

1、FPGA的时钟输入要使用全局时钟引脚。高热下时钟漂移,要加锁相环同步电路。FPGA全部用同步设计,不直接用组合逻辑。

2、晶振参考最小化设计,电源部分需要加磁珠和小电容去耦,输出加始端匹配(频率不高就不用加匹配,远端有时也要加匹配,防反射)。

关于晶振位置的补充说明:

为了避免晶振受到PCB边缘的干扰,通常可以采取以下措施:将晶振放置在离PCB边缘一定距离的位置,以减少外界干扰的影响;在晶振周围设置合适的屏蔽罩,以减少外界电磁辐射的影响;考虑机械固定的问题,避免晶振受到机械振动的影响;合理规划晶振的布局,避免与其他元器件产生电磁干扰;合理规划散热措施,以减少温度变化对晶振的影响。