晶诺威科技产有源晶振如何连接芯片?

连接有源晶振(Crystal Oscillator)相对于无源晶振来说要简单很多,因为其内部已经集成了振荡电路,可以直接输出稳定的时钟信号。

核心思想:

将有源晶振视为一个“时钟信号发生器”,芯片是一个“时钟信号接收者”。一个标准的有源晶振(如四脚贴片封装)通常有四个引脚:

1. VCC:电源引脚(通常为3.3V或5V,具体看型号)。

2. GND:接地引脚。

3. OUT:时钟信号输出引脚(有些型号标记为 CLK 或 OUTPUT)。

4. NC:空脚(内部不连接,或有时是使能引脚OE)。

最关键、最简单的连接就是:将有源晶振的 OUT 引脚直接连接到芯片的时钟输入引脚(如 XTAL_IN、 CLK_IN 等)。

连接步骤详解:

1. 供电(最关键的一步)

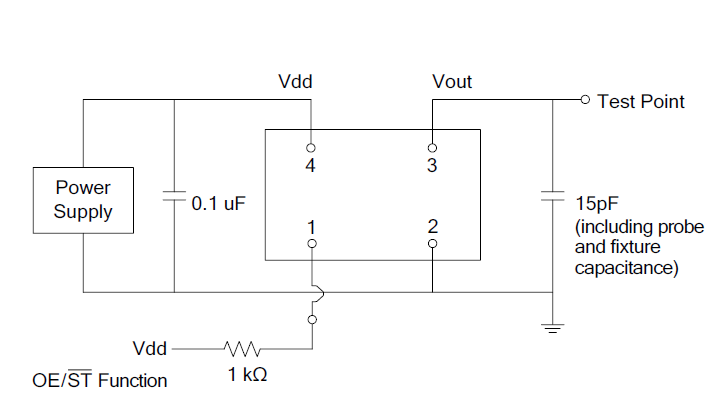

将晶振的 VCC 引脚连接到系统的干净电源(例如 3.3V)。建议在VCC引脚附近放置一个0.1μF(100nF)的陶瓷去耦电容到地,用于滤除电源噪声,确保振荡器稳定工作。有时还会并联一个更大的电容(如10μF)。

2. 接地

将晶振的 GND 引脚连接到系统的数字地(GND),确保地回路良好。

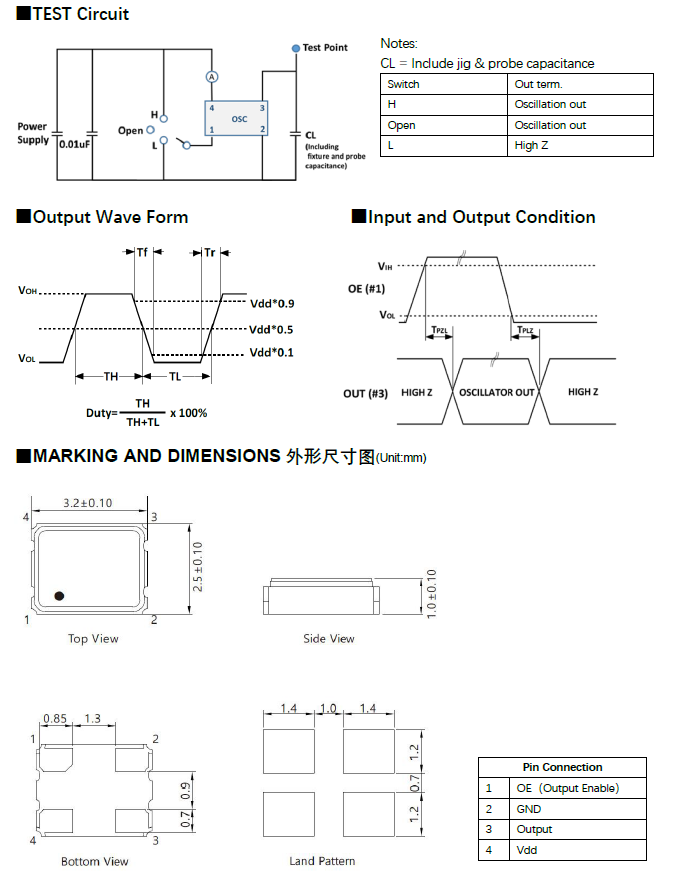

晶诺威科技产有源晶振测试电路

3. 信号输出

将晶振的 OUT 引脚连接到芯片的外部时钟输入引脚。注意芯片手册命名:这个引脚可能叫 XTAL_IN、EXTAL、OSC_IN、CLK_IN 等。

4. 空引脚/使能引脚

- NC 引脚:悬空即可,什么都不用接。

- OE 引脚:如果是有输出使能的型号,通常需要上拉到 VCC 以启用输出,或通过 MCU GPIO 控制。

PCB布局布线注意事项(影响稳定性)

良好的布线能避免时钟不稳定、辐射超标等问题。

1. 远离干扰源:使晶振和走线远离高频、高噪声的元件(如开关电源、电感、高速数据线)。

2. 短线为上策:时钟输出线尽可能短而直,减少天线效应和信号衰减。

3. 用地平面包围:在时钟信号线周围用接地铜皮进行“包地”处理,可以屏蔽干扰。

4. 禁止在底层走线:时钟线尽量不要使用过孔换层,更不要走在PCB底层,以免引入更多干扰。

5. 串联电阻:如原理图所示,在输出线上串联一个 22Ω – 100Ω 的小电阻(靠近晶振端),可以抑制过冲、振铃,并减少谐波辐射。

6. 末端匹配:对于频率很高(如 > 50MHz)或走线较长的时钟,可能在接收端(芯片引脚)对地接一个 10pF – 30pF 的小电容,或进行阻抗匹配,具体看芯片要求。