关于RTC晶振受干扰问题,晶诺威科技分析三点如下:

RTC晶振(32.768kHz)受到干扰,是硬件设计中最常见也最让人头疼的问题之一。由于它本身是一个高阻抗、低功耗、小信号的敏感器件,非常容易受到外部电磁信号和PCB布局的干扰。

1、走时不准

不良具体表现:时钟变快或变慢(通常是变快)

原因分析:高频干扰信号叠加在晶振信号上,被RTC电路误判为额外的时钟脉冲,导致计数偏多。

2、死机/停振

不良具体表现:时间停止,重新上电或复位后恢复

具体表现:强干扰导致振荡电路工作点偏移,无法维持振荡,或因噪声触发芯片内部保护或逻辑紊乱。

3、波形畸变

不良具体表现:示波器测量时波形杂乱、幅度异常 | 探头引入的电容负载破坏了谐振状态,或空间电磁干扰直接耦合进测量回路。

针对这些症状,可以从以下几个方面排查和解决:

1、优化PCB布局,这是最重要、最根本的环节。

![]() 缩短走线:将晶振和两个负载电容尽可能贴近RTC芯片的XIN和XOUT引脚放置,让走线越短越好。

缩短走线:将晶振和两个负载电容尽可能贴近RTC芯片的XIN和XOUT引脚放置,让走线越短越好。

![]() 避免干扰:晶振下方及其相关走线的区域,禁止走数字信号线,尤其是高频信号线(如SPI、I2C、射频线)。

避免干扰:晶振下方及其相关走线的区域,禁止走数字信号线,尤其是高频信号线(如SPI、I2C、射频线)。

![]() 包地/铺铜:在晶振外围打上一圈过孔,连接到地平面,形成一个“保护环”。晶振下方最好铺上完整的地平面,不要跨分割。

包地/铺铜:在晶振外围打上一圈过孔,连接到地平面,形成一个“保护环”。晶振下方最好铺上完整的地平面,不要跨分割。

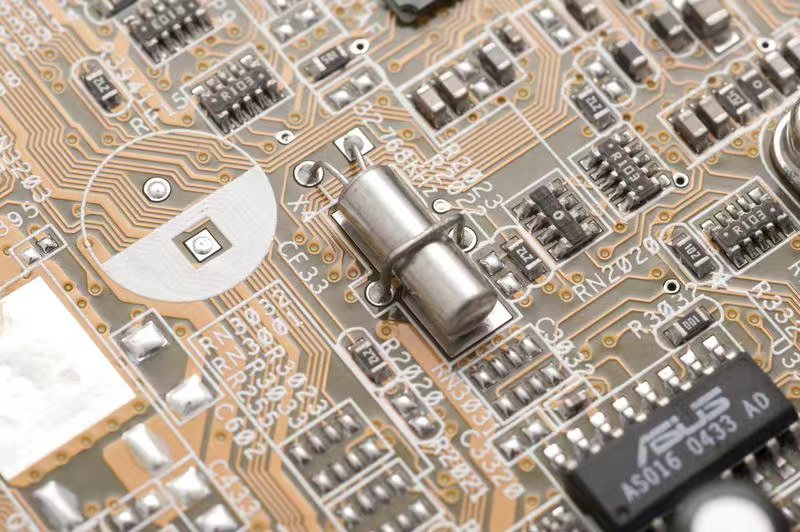

![]() 外壳接地:对于金属封装的圆柱形晶振(如常见的32.768kHz音叉晶振),建议尝试将金属外壳接地,这能起到非常好的屏蔽作用。如下图所示:

外壳接地:对于金属封装的圆柱形晶振(如常见的32.768kHz音叉晶振),建议尝试将金属外壳接地,这能起到非常好的屏蔽作用。如下图所示:

2、 外围保障:合理的电路设计

![]() 负载电容匹配:确保外接的负载电容(C1、C2)计算正确,使晶振工作在标称频率上。参数不准会降低电路的稳定性,使其更容易受干扰停振。

负载电容匹配:确保外接的负载电容(C1、C2)计算正确,使晶振工作在标称频率上。参数不准会降低电路的稳定性,使其更容易受干扰停振。

![]() 加装旁路(by-pass)电容:如果板上干扰源无法避免,可以在RTC的电源引脚(VDD)上加一个0.1μF的旁路电容,并靠近引脚放置,滤除电源上的高频噪声。

加装旁路(by-pass)电容:如果板上干扰源无法避免,可以在RTC的电源引脚(VDD)上加一个0.1μF的旁路电容,并靠近引脚放置,滤除电源上的高频噪声。

![]() 观察波形:重点关注波形是否干净、正弦波是否光滑。如果波形上叠加有毛刺或不规则抖动,说明受到了干扰。

观察波形:重点关注波形是否干净、正弦波是否光滑。如果波形上叠加有毛刺或不规则抖动,说明受到了干扰。

![]() 如果PCB空间紧张,或者对走时精度和抗干扰要求极高,最彻底的方案是换用有源晶振,优点是抗干扰能力极强,无需复杂的PCB布局考虑。

如果PCB空间紧张,或者对走时精度和抗干扰要求极高,最彻底的方案是换用有源晶振,优点是抗干扰能力极强,无需复杂的PCB布局考虑。

![]() 如果频率精度要求更高,可以选择TCXO温补晶振,其频率精度可达±0.5ppm,工作温度范围为-40~+85℃。

如果频率精度要求更高,可以选择TCXO温补晶振,其频率精度可达±0.5ppm,工作温度范围为-40~+85℃。