一般来说,不管是无源晶振,还是有源晶振,它与芯片之间的距离需要尽量缩短。时钟信号源通常是系统中最严重的EMI(Electromagnetic Interference 电磁干扰)辐射源。如果接长线,就容易造成长线变成天线的问题,这显然会导致在很多应用中的禁止,所以时钟信号源都必须尽量靠近相关元器件。在需要多个时钟信号源的情况下,可以采用多层电路板将时钟连线屏蔽的办法。有源晶振的输出一般是标准TTL规格,能驱动几个芯片需要根据芯片自身特性而定。

关于晶振该如何合理布线,晶诺威科技建议如下:

1、电路尽量短,与其它信号需要20mil的间距,最好采用接地与其他信号隔离。

2、晶振下面不可走线,尽量缩短电路中与芯片端的距离。

3、晶振底下尽量不要走线。如果必须要走线,不能走线进入晶振焊脚50mil范围之内,尤其是要避免高速讯号的冲击。

晶振信号电路尽可能缩短,需要接地,因为晶振工作时会产生噪声,所以从根本上就是避免它工作时影响到其它元器件,或者避免别的元器件工作时干扰到它。另外,建议尽可能不要在电路板上穿孔走线,因为每个过孔会有产生0.5pF的寄生电容。最后需要注意,走线粗细需要具有一致性。

拓展阅读:如何有效提升晶振的抗干扰能力可以采取以下措施

在实际应用中,晶振作为频率控制元件,其稳定性和准确性至关重要。然而,晶振容易受到电磁干扰、射频干扰以及电源噪声等外部因素的影响,导致其频率稳定性下降。为了确保晶振的频率稳定性,必须采取有效的抗干扰措施。

晶振受到的干扰主要包括电磁干扰、射频干扰和电源噪声。电磁干扰是由外部电磁场或其他设备产生的辐射或噪声引起的,可能导致晶振工作异常或信号失真。射频干扰主要由无线通信设备、雷达、Wi-Fi路由器、手机等产生的射频信号造成,通过辐射或耦合进入晶振电路,影响其正常的振荡和频率输出。电源噪声是由电源的不稳定性或其他设备的干扰产生的,通过电源线路传导到晶振电路中,影响晶振稳定的频率输出。

为了提升晶振的抗干扰能力,可以采取以下措施:

1、选择合适的晶振型号:低相位噪声、低电磁干扰和低射频干扰晶振是提升抗干扰能力的关键。这些晶振型号具有较低的相位噪声和电磁干扰,能够更好地抵抗外部干扰。

2、使用晶体滤波器:晶体滤波器能够有效抑制高频噪声,降低干扰对晶振的影响。通过选择合适的滤波器,可以滤除干扰信号,提高晶振的频率稳定性。

3、采用金属屏蔽外壳:金属屏蔽外壳可以防止电磁辐射进入晶振电路,提高抗干扰性能。通过将晶振封装在金属外壳中,可以减少外部电磁干扰对晶振的影响。

4、优化电路设计:合理的PCB布局能够有效降低干扰耦合,减少外部信号对晶振的影响。尽量减少长引线和高频噪声路径,避免信号反射和干扰。通过优化电路设计,可以降低干扰对晶振的影响,提高其频率稳定性。

5、去耦与稳压:在电源输入端加入去耦电容,以减少电源波动和噪声干扰。同时使用稳压电路,确保晶振获得稳定的电源供给,避免电压波动影响其频率稳定性。通过去耦和稳压措施,可以降低电源噪声对晶振的影响,提高其频率稳定性。

6、应用软件抗干扰技术:通过数字滤波算法进一步降低噪声干扰的影响。对采集到的信号进行数字处理,软件滤波器可以消除外部干扰,提高信号的纯净度和稳定性。通过应用软件抗干扰技术,可以进一步降低干扰对晶振的影响,提高其频率稳定性。

综上所述,晶振的抗干扰技术对于确保其频率稳定性至关重要。通过选择合适的晶振型号、使用晶体滤波器、采用金属屏蔽外壳、优化电路设计、去耦与稳压以及应用软件抗干扰技术,可以有效地抵抗电磁干扰、射频干扰和电源噪声的影响,提高晶振的频率稳定性。

拓展阅读:晶振电路之近端和远端相位噪声

近端相位噪声

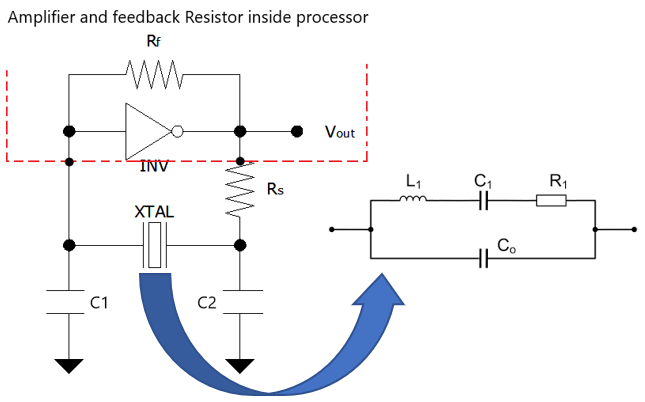

近端相位噪声通常指距离载波频率较近的频率范围内的噪声水平。这一区域的噪声主要由晶体本身的参数决定,包括晶体的谐振频率、品质因数(Q值)、等效串联电阻(ESR)等。

谐振频率:晶体的谐振频率决定了其工作的基本频率,是晶振性能的基础。

品质因数(Q值):晶体的Q值越高,其频率稳定性越好,近端相位噪声通常越低。高Q值的晶体谐振电阻较小,因此起振速度更快,有助于降低近端相噪。

等效串联电阻(ESR):ESR反映了晶体在振荡过程中的能量损耗。较小的ESR有助于减少能量损失,提高振荡信号的稳定性和强度,从而降低近端相噪。

此外,晶体的制造工艺和材料也会对近端相位噪声产生影响。优质的制造工艺和材料能够减少晶体内部的缺陷和杂质,从而降低噪声水平。

远端相位噪声

远端相位噪声则指距离载波频率较远的频率范围内的噪声水平。这一区域的噪声更多地依赖于晶体匹配的振荡IC(集成电路)的特性。

振荡IC的设计:振荡IC的设计,包括放大器的噪声水平、电源噪声抑制能力、电路布局等,都会对远端相位噪声产生影响。良好的振荡IC设计可以有效地降低远端相位噪声。

电源噪声:电源噪声是远端相噪的重要来源之一。通过增加电源去耦电容、优化电源管理等方式,可以有效地减少电源噪声对远端相噪的影响。

电路布局:合理的电路布局可以减少信号干扰和延迟,确保晶振信号的完整性,从而降低远端相噪。

电性能参数对近端远端相噪的综合影响

在晶振电路设计中,起振时间、负载电容等电性能参数也对近端和远端相位噪声有重要影响。

起振时间:起振时间的长短主要由晶体的谐振电阻和振荡器的负性阻抗共同决定。高Q值的晶体谐振电阻较小,起振速度更快。

负载电容(CL):负载电容的大小不仅影响振荡器的负性阻抗,还会对近端和远端相噪带来不同的影响。较小的负载电容使负性阻抗变大,起振速度更快,牵引量更大,但同时也更容易受到杂散电容的影响。这对近端相噪有利,但可能增加远端相噪。较大的负载电容则相反,有助于提升远端相噪的稳定性,但可能对近端相噪不利。