如何调整晶振电路的负性阻抗Negative Resistance Value?晶诺威科技解释如下:

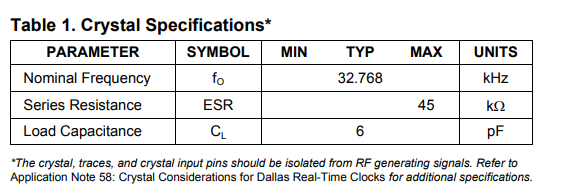

一般而言,负性阻抗值应满足不少于晶振标称最大阻抗(ESR/Equivalent Series Resistance/等效串联电阻)的3~5倍。如:若32.768KHz晶振ESR=45KΩ,则建议负性阻抗Negative Resistance Value在200kΩ以上。由此可见,在无源晶振起振电路中,负性阻抗的大小直接决定着晶振的起振能力。

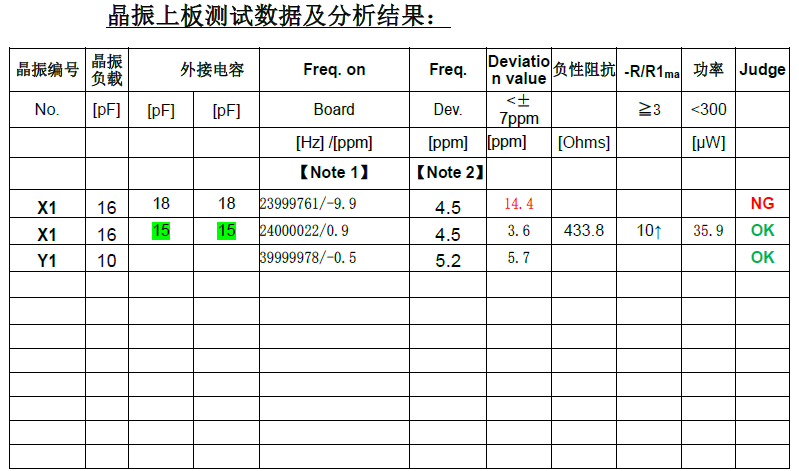

- 如果负性阻抗(余量)过大,可以尝试通过将晶振外接电容C1和C2的值调大来降低负性阻抗。

- 如果负性阻抗(余量)太小,可以尝试选择较小ESR的晶振或将晶振外接电容C1和C2的值调小来实现增大负性阻抗的目的。

注:

- 如果无源晶振不起振,我们不建议通过提高其额定激励功率(Drive Level)来解决该问题,原因是过高激励功率会造成晶振过驱,导致晶振频率不稳定或损坏。一般32.768KHz晶振激励功率为0.1μW~0.2μW。

- 如果无源晶振不挂外接电容,可能造成晶振频率输出不稳定。

拓展阅读:无源晶振起振电路中为什么需要负阻抗?

在普通电路中,电阻是消耗能量的。但在振荡电路中,放大器通过反馈网络可以表现出一种等效的“负电阻”特性,向晶体提供能量以补偿其损耗。

石英晶体本质上是一个高Q值的谐振器,但它自身存在等效串联电阻ESR,如果没有外部电路补偿能量,振荡会迅速衰减直至停止。因此,回路中的负电阻绝对值|−R|必须大于晶体的等效串联电阻RR。

什么是起振裕量?

起振裕量可以理解为振荡电路所提供的负电阻能力,相对于晶体损耗电阻的“宽裕程度”。建议振荡宽限为晶振等效串联电阻RR的5倍之上:│−R│ ≥ 5 × RR当振荡进入稳定状态后,系统能量达到动态平衡,关系趋近于:RR ≈ │−R│

起振裕量不足会带来什么问题?

在实际产品中,起振裕量不足往往不是“完全不起振”,而是表现为各种隐性故障:上电偶发不起振冷启动失败高温或低温停振批量一致性差使用一段时间后,老化停振负电阻的测量方法负电阻测量的方法是在晶体一端串联一个测试电阻Rtest(建议使用低感抗电阻),逐步增加阻值,直到振荡刚好停止。负电阻 ≈ Rtest + 晶体 RL该数值反映了振荡电路的实际负阻能力。这种方法是评估MCU内部振荡能力的常用手段。

起振裕量也不是越大越好。虽然裕量越大越容易起振,但过高也会带来副作用:如:功耗增加、相位噪声恶化、频率稳定性下降、晶体过驱动导致寿命缩短等问题。

采购晶振建议

1、考虑影响稳定性的参数:ESR,负载电容,激励功率,工作温度范围,老化率等;

2、关注晶振等效串联电阻ESR上限而非典型值:规格书中的Typical(典型)值只代表平均水平,Max.(最大值)才决定可能性风险;

3、避免随意替代型号:即使频率、尺寸、ppm相同,只要ESR或CL不一致,就可能导致晶振不能起振;

4、低价晶振的隐性成本:低价晶振常见问题有ESR离散大;批次一致性差;老化快;高温停振等。