-

; ) 四脚及两脚无源晶振布线图例

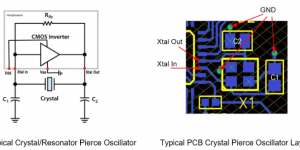

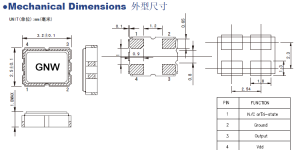

四脚及两脚无源晶振焊盘图: 四脚及两脚无源晶振内部结构图: 在PCB布线时,为了避免晶振输出的频率信号受干扰或减弱,建议无源晶振(晶体谐振器)的一对信号线要走成类差分的形式,走线尽量短、且要加粗并进行包地处理,效果如下图所示: 注:无源晶振的两个管脚(信号输入脚与信号输出…时间:2023/04/05

四脚及两脚无源晶振布线图例

四脚及两脚无源晶振焊盘图: 四脚及两脚无源晶振内部结构图: 在PCB布线时,为了避免晶振输出的频率信号受干扰或减弱,建议无源晶振(晶体谐振器)的一对信号线要走成类差分的形式,走线尽量短、且要加粗并进行包地处理,效果如下图所示: 注:无源晶振的两个管脚(信号输入脚与信号输出…时间:2023/04/05 -

; ) 晶体布线设计指南

Crystal Printed Circuit Board (PCB) Design Guidelines晶体布线设计指南 Connect the crystal and external load capacitors on the PCB as close as possible to the …时间:2022/10/14

晶体布线设计指南

Crystal Printed Circuit Board (PCB) Design Guidelines晶体布线设计指南 Connect the crystal and external load capacitors on the PCB as close as possible to the …时间:2022/10/14 -

; ) 晶体振荡器布线设计指导

Oscillator Printed Circuit Board (PCB) Design Guidelines晶体振荡器布线设计指导 Layout the oscillator footprint on the PCB as close as possible to the input pins…时间:2022/10/12

晶体振荡器布线设计指导

Oscillator Printed Circuit Board (PCB) Design Guidelines晶体振荡器布线设计指导 Layout the oscillator footprint on the PCB as close as possible to the input pins…时间:2022/10/12 -

; ) 晶振下方可以走线吗?

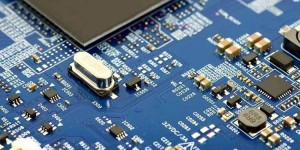

晶振下方可以走线吗? 答:不可以! 晶振下方不可以走线。另外,晶振布放和走线同IC应在相同层(走线过程不能隔断,不要过孔换层)。时钟线路尽量短,防止形成发射天线,引发信号之间干扰。时间:2022/07/19

晶振下方可以走线吗?

晶振下方可以走线吗? 答:不可以! 晶振下方不可以走线。另外,晶振布放和走线同IC应在相同层(走线过程不能隔断,不要过孔换层)。时钟线路尽量短,防止形成发射天线,引发信号之间干扰。时间:2022/07/19 -

; ) 晶振抗干扰电路:电源,信号线,GND及隔离区设计说明

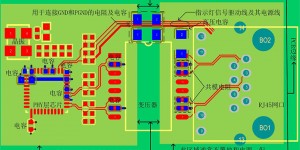

(晶振抗干扰电路:关于电源,信号线,GND及隔离区图示) 晶振抗干扰电路设计时,请注意以下六点: 1、在晶振布线时,尽量将晶振靠近芯片方式、缩短布线长度,匹配电容也一样 2、晶振走线要直 3、晶振走线不能有过孔 4、晶振位置不要靠近高压,大电流的电源走线 5、有源晶振一般比无源晶振抗干扰能力更强,因…时间:2022/05/31

晶振抗干扰电路:电源,信号线,GND及隔离区设计说明

(晶振抗干扰电路:关于电源,信号线,GND及隔离区图示) 晶振抗干扰电路设计时,请注意以下六点: 1、在晶振布线时,尽量将晶振靠近芯片方式、缩短布线长度,匹配电容也一样 2、晶振走线要直 3、晶振走线不能有过孔 4、晶振位置不要靠近高压,大电流的电源走线 5、有源晶振一般比无源晶振抗干扰能力更强,因…时间:2022/05/31 -

; ) 如何减少电路板寄生电容对贴片晶振的影响?

如何减少电路板寄生电容对贴片晶振的影响? 措施:针对多层板,建议挖空晶振下方的平面层。 原因分析: 如果贴片晶振焊盘下方存在寄生电容过大,则会直接导致晶振频偏或输出频率不稳定,引发电子设备功能性不良。 在常温之下。PCB板工作时可能不会出现问题,但是在一些高低温的条件下,寄生电容就会增加或不稳定,这…时间:2022/05/18

如何减少电路板寄生电容对贴片晶振的影响?

如何减少电路板寄生电容对贴片晶振的影响? 措施:针对多层板,建议挖空晶振下方的平面层。 原因分析: 如果贴片晶振焊盘下方存在寄生电容过大,则会直接导致晶振频偏或输出频率不稳定,引发电子设备功能性不良。 在常温之下。PCB板工作时可能不会出现问题,但是在一些高低温的条件下,寄生电容就会增加或不稳定,这…时间:2022/05/18 -

; ) 喇叭或蜂鸣器会干扰晶振正常工作吗?

喇叭或蜂鸣器会干扰晶振正常工作吗? 答:会!喇叭或蜂鸣器会干扰晶振正常工作。 任何周期性物理冲击或机械振动都会对晶振的输出频率及/或幅度造成不同程度的影响,比如:马达、压电扬声器、压电蜂鸣器、喇叭等。 当晶振的正常工作受到此类干扰时,可能造成设备工作不正常,如果是通信器材,则可能会发生通信故障。 在…时间:2022/04/22

喇叭或蜂鸣器会干扰晶振正常工作吗?

喇叭或蜂鸣器会干扰晶振正常工作吗? 答:会!喇叭或蜂鸣器会干扰晶振正常工作。 任何周期性物理冲击或机械振动都会对晶振的输出频率及/或幅度造成不同程度的影响,比如:马达、压电扬声器、压电蜂鸣器、喇叭等。 当晶振的正常工作受到此类干扰时,可能造成设备工作不正常,如果是通信器材,则可能会发生通信故障。 在…时间:2022/04/22 -

; ) 降低晶振振荡电路中EMI的解决方案是什么?

Electromagnetic interference (or EMI, also called radio frequency interference or RFI) is a (usually undesirable) disturbance that affects an electric…时间:2022/04/11

降低晶振振荡电路中EMI的解决方案是什么?

Electromagnetic interference (or EMI, also called radio frequency interference or RFI) is a (usually undesirable) disturbance that affects an electric…时间:2022/04/11 -

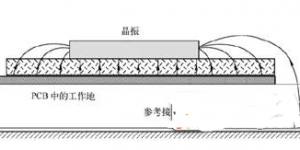

; ) 为何晶振布置在PCB边缘时会导致辐射超标?

为何晶振布置在PCB边缘时会导致辐射超标? 如上图所示:当晶振布置在PCB中间或离PCB边缘较远时,由于PCB中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地(GND)之间,即在PCB内部,分布到参考接地板的电场大大减小,从而导致晶振与参考接地板之间的寄生电容大大减小。反之,若晶振布置…时间:2022/02/22

为何晶振布置在PCB边缘时会导致辐射超标?

为何晶振布置在PCB边缘时会导致辐射超标? 如上图所示:当晶振布置在PCB中间或离PCB边缘较远时,由于PCB中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地(GND)之间,即在PCB内部,分布到参考接地板的电场大大减小,从而导致晶振与参考接地板之间的寄生电容大大减小。反之,若晶振布置…时间:2022/02/22 -

; ) 抗电磁信号干扰:晶振接地GND说明

在数字电路设计之初,为了降低电路之间的互相干扰,一般我们会引入不同的GND地线来作为不同功能电路的0V参考点,形成不同的电流回路。 电路板上GND地线的分类如下: 1. 模拟地线AGND 2. 数字地线DGND 3. 功率地线PGND 4. 电源地线GND 5. 交流地线CGND 6. 大地地线EG…时间:2022/02/21

抗电磁信号干扰:晶振接地GND说明

在数字电路设计之初,为了降低电路之间的互相干扰,一般我们会引入不同的GND地线来作为不同功能电路的0V参考点,形成不同的电流回路。 电路板上GND地线的分类如下: 1. 模拟地线AGND 2. 数字地线DGND 3. 功率地线PGND 4. 电源地线GND 5. 交流地线CGND 6. 大地地线EG…时间:2022/02/21