-

; ) 晶振频率不稳定原因及解决办法

(晶振频率不稳定原因:老化、飘移和短稳) 关于晶振频率不稳定原因及解决办法,晶诺威科技解释如下: 造成晶振频率不稳定的主要因素有三种:老化、飘移和短稳。在晶振使用过程中,除上面提到的三个因素之外,若晶振出现频率不稳定现象,晶诺威科技建议如下: 1、 选择正规晶振厂家晶振产品,从根部消除因晶振本身质量…时间:2021/09/18

晶振频率不稳定原因及解决办法

(晶振频率不稳定原因:老化、飘移和短稳) 关于晶振频率不稳定原因及解决办法,晶诺威科技解释如下: 造成晶振频率不稳定的主要因素有三种:老化、飘移和短稳。在晶振使用过程中,除上面提到的三个因素之外,若晶振出现频率不稳定现象,晶诺威科技建议如下: 1、 选择正规晶振厂家晶振产品,从根部消除因晶振本身质量…时间:2021/09/18 -

; ) 晶振为何要尽可能靠近IC管脚?

晶振和 IC 间一般通过铜质走线相连,可以看成一段导线或数段导线,导线在切割磁力线时会产生电流,导线越长,产生的电流越强,因此产生的电能量就越强,直到接收到的电信号强度超过或接近晶振产生的信号强度时,IC内的放大电路输出的将不再是固定频率的方波,而是根本不需要的杂散信号,导致数字电路时钟无法同步工作…时间:2021/09/12

晶振为何要尽可能靠近IC管脚?

晶振和 IC 间一般通过铜质走线相连,可以看成一段导线或数段导线,导线在切割磁力线时会产生电流,导线越长,产生的电流越强,因此产生的电能量就越强,直到接收到的电信号强度超过或接近晶振产生的信号强度时,IC内的放大电路输出的将不再是固定频率的方波,而是根本不需要的杂散信号,导致数字电路时钟无法同步工作…时间:2021/09/12 -

; ) 为什么用手触摸一下晶振就会起振?

一般这种情况发生在无源晶振的电路应用,原因分析为连接晶振模块(包括匹配电容)和主芯片引线过长会增加寄生电容,同时更加容易受到静电干扰以及其它信号线的串扰。晶振在频率范围的临界点(边缘值)振荡,造成芯片无法正常捕捉到晶振频率信号。 用手触摸晶振时,手上自带的静电或手本身作为一个电容器改变了电路板的杂散…时间:2021/09/06

为什么用手触摸一下晶振就会起振?

一般这种情况发生在无源晶振的电路应用,原因分析为连接晶振模块(包括匹配电容)和主芯片引线过长会增加寄生电容,同时更加容易受到静电干扰以及其它信号线的串扰。晶振在频率范围的临界点(边缘值)振荡,造成芯片无法正常捕捉到晶振频率信号。 用手触摸晶振时,手上自带的静电或手本身作为一个电容器改变了电路板的杂散…时间:2021/09/06 -

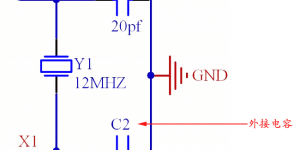

; ) 如何设计无源晶振及两颗外接电容在PCB的最佳位置?

无源晶振及两颗外接电容在PCB的位置 两颗外接电容应尽量靠近晶振引脚(频率输入脚与频率输出脚)设计。 晶振核心部件为石英晶体,容易受外力撞击或跌落影响而破碎。在PCB布线时最好不要把晶振设计在PCB边缘,尽量使其靠近芯片。 晶振走线需要用GND保护稳妥,远离敏感信号源,如RF及高速信号,以免频率信号…时间:2021/08/17

如何设计无源晶振及两颗外接电容在PCB的最佳位置?

无源晶振及两颗外接电容在PCB的位置 两颗外接电容应尽量靠近晶振引脚(频率输入脚与频率输出脚)设计。 晶振核心部件为石英晶体,容易受外力撞击或跌落影响而破碎。在PCB布线时最好不要把晶振设计在PCB边缘,尽量使其靠近芯片。 晶振走线需要用GND保护稳妥,远离敏感信号源,如RF及高速信号,以免频率信号…时间:2021/08/17 -

; ) 如何减少寄生电容对晶振造成的辐射干扰?

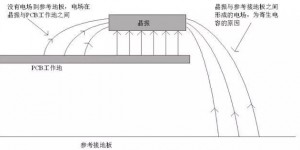

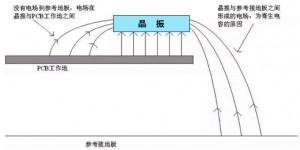

若晶振正好布线于电路板边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶振与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越…时间:2021/06/15

如何减少寄生电容对晶振造成的辐射干扰?

若晶振正好布线于电路板边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶振与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越…时间:2021/06/15 -

; ) PCB板时钟晶振及相关元件布线原则归纳总结

1、晶振电路连线精简原则 连线精简,尽可能短,力求线条简单明了。 2.晶振电路安全载流原则 铜线的宽度应以自己所能承载的电流为基础进行设计,铜线的载流能力取决于以下因素:线宽、线厚(铜铂厚度)、允许温升等。 3.晶振电路电磁抗干扰原则 电磁抗干扰原则涉及的知识点比较多,例如铜膜线的拐弯处应为圆角或斜…时间:2020/10/19

PCB板时钟晶振及相关元件布线原则归纳总结

1、晶振电路连线精简原则 连线精简,尽可能短,力求线条简单明了。 2.晶振电路安全载流原则 铜线的宽度应以自己所能承载的电流为基础进行设计,铜线的载流能力取决于以下因素:线宽、线厚(铜铂厚度)、允许温升等。 3.晶振电路电磁抗干扰原则 电磁抗干扰原则涉及的知识点比较多,例如铜膜线的拐弯处应为圆角或斜…时间:2020/10/19 -

; ) 如何降低电磁对晶振时钟信号的干扰

电磁三要素是电磁干扰源、被干扰对象和传播电磁干扰的途径。PCB板上安装的时钟信号是一种引起PCB板电磁兼容问题的常见而又非常重要的辐射源。尽管时钟信号与其他数据信号、控制信号的逻辑电平一般都是一样的,翻转速率一般也没有太大的差别(大多数总线数据率与时钟信号翻转速率之比是1:1或者1:2),但由于时钟…时间:2020/09/15

如何降低电磁对晶振时钟信号的干扰

电磁三要素是电磁干扰源、被干扰对象和传播电磁干扰的途径。PCB板上安装的时钟信号是一种引起PCB板电磁兼容问题的常见而又非常重要的辐射源。尽管时钟信号与其他数据信号、控制信号的逻辑电平一般都是一样的,翻转速率一般也没有太大的差别(大多数总线数据率与时钟信号翻转速率之比是1:1或者1:2),但由于时钟…时间:2020/09/15 -

; ) 晶振位于线路板边缘会带来哪些隐患?

如果晶振布置在了线路板边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与实验室中参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶体与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电…时间:2020/09/14

晶振位于线路板边缘会带来哪些隐患?

如果晶振布置在了线路板边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与实验室中参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶体与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电…时间:2020/09/14 -

; ) 晶振外接电容的作用与选择

在使用外部晶振作为芯片的时钟信号源时,晶振的两个引脚需要分别串联两颗与之匹配的电容。千万不要小窥这两颗电容,如果没有它们,一般情况下晶振就无法正常工作。原理如下: 芯片晶振引脚的内部通常是一个反相器,芯片晶振的两个引脚之间还需要连接一个电阻,使反相器在振荡初始时处与线性状态,但这个电阻一般集成在芯片…时间:2020/09/03

晶振外接电容的作用与选择

在使用外部晶振作为芯片的时钟信号源时,晶振的两个引脚需要分别串联两颗与之匹配的电容。千万不要小窥这两颗电容,如果没有它们,一般情况下晶振就无法正常工作。原理如下: 芯片晶振引脚的内部通常是一个反相器,芯片晶振的两个引脚之间还需要连接一个电阻,使反相器在振荡初始时处与线性状态,但这个电阻一般集成在芯片…时间:2020/09/03 -

; ) 晶振怎么布线更合理

一般来说,不管是无源晶振,还是有源晶振,它与芯片之间的距离需要尽量缩短。时钟信号源通常是系统中最严重的EMI(Electromagnetic Interference 电磁干扰)辐射源。如果接长线,就容易造成长线变成天线的问题,这显然会导致在很多应用中的禁止,所以时钟信号源都必须尽量靠近相关元器件。…时间:2020/05/20

晶振怎么布线更合理

一般来说,不管是无源晶振,还是有源晶振,它与芯片之间的距离需要尽量缩短。时钟信号源通常是系统中最严重的EMI(Electromagnetic Interference 电磁干扰)辐射源。如果接长线,就容易造成长线变成天线的问题,这显然会导致在很多应用中的禁止,所以时钟信号源都必须尽量靠近相关元器件。…时间:2020/05/20