-

; ) 激励功率过大会导致晶体不起振吗?

激励功率过大会导致晶体不起振吗? 答:是的,激励功率过大的确会导致晶体不起振,甚至造成永久性损坏。 可以把晶体看作一个需要精确能量驱动的"心脏"。激励功率就像是驱动它的"能量": 能量过小(欠激励):心脏跳动无力,无法启动,导致晶体不起振。 能量过大(过激励):这是导致晶体不起振的一个关键原因。过大…时间:2026/04/04

激励功率过大会导致晶体不起振吗?

激励功率过大会导致晶体不起振吗? 答:是的,激励功率过大的确会导致晶体不起振,甚至造成永久性损坏。 可以把晶体看作一个需要精确能量驱动的"心脏"。激励功率就像是驱动它的"能量": 能量过小(欠激励):心脏跳动无力,无法启动,导致晶体不起振。 能量过大(过激励):这是导致晶体不起振的一个关键原因。过大…时间:2026/04/04 -

; ) 晶振的限流电阻太大会有什么影响?

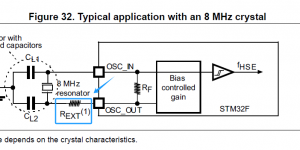

晶振的限流电阻太大会有什么影响? 在数字电路中,为晶振的OSC_OUT引脚串接的限流电阻(Rext或Rd或Rs),通常称为串联电阻或阻尼电阻。如果取值过大,可能会产生一系列负面影响。 这个电阻的主要作用通常是: 限制驱动电流,防止芯片内部的振荡器电路对晶振产生过驱动。 提供阻尼,抑制高次谐波,使振荡…时间:2026/03/09

晶振的限流电阻太大会有什么影响?

晶振的限流电阻太大会有什么影响? 在数字电路中,为晶振的OSC_OUT引脚串接的限流电阻(Rext或Rd或Rs),通常称为串联电阻或阻尼电阻。如果取值过大,可能会产生一系列负面影响。 这个电阻的主要作用通常是: 限制驱动电流,防止芯片内部的振荡器电路对晶振产生过驱动。 提供阻尼,抑制高次谐波,使振荡…时间:2026/03/09 -

; ) 晶振电路:等效串联电阻ESR和串联电阻的区别是什么?

(串联电阻 VS 等效串联电阻) 晶振电路:等效串联电阻ESR和串联电阻的区别是什么? 无源晶振,即晶体谐振器,晶体属于半导体器件。用万用表测试无源晶振单体,其频率管脚之间是不导通的。等效串联电阻ESR是一个“等效”出来的、虚拟的模型参数,用来描述一个非理想元件的损耗特性。换句话说,ESR是计算出来…时间:2026/01/18

晶振电路:等效串联电阻ESR和串联电阻的区别是什么?

(串联电阻 VS 等效串联电阻) 晶振电路:等效串联电阻ESR和串联电阻的区别是什么? 无源晶振,即晶体谐振器,晶体属于半导体器件。用万用表测试无源晶振单体,其频率管脚之间是不导通的。等效串联电阻ESR是一个“等效”出来的、虚拟的模型参数,用来描述一个非理想元件的损耗特性。换句话说,ESR是计算出来…时间:2026/01/18 -

; ) CMOS输出的晶振能直接连接LVTTL逻辑吗?

CMOS输出的晶振能接LVTTL逻辑吗? 可以,但通常需要串联一个电阻。 一、电平标准回顾 CMOS输出晶振: 通常指输出电平符合CMOS逻辑标准的晶振。对于3.3V供电的晶振,其输出高电平(Voh)非常接近3.3V,低电平(Vol)非常接近0V。它的输出驱动能力较强,边沿非常陡峭。 LVTTL输入…时间:2025/11/08

CMOS输出的晶振能直接连接LVTTL逻辑吗?

CMOS输出的晶振能接LVTTL逻辑吗? 可以,但通常需要串联一个电阻。 一、电平标准回顾 CMOS输出晶振: 通常指输出电平符合CMOS逻辑标准的晶振。对于3.3V供电的晶振,其输出高电平(Voh)非常接近3.3V,低电平(Vol)非常接近0V。它的输出驱动能力较强,边沿非常陡峭。 LVTTL输入…时间:2025/11/08 -

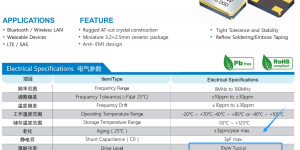

; ) 晶振Drive Level 10μW Typ. 100μW. Max.是什么意思?

晶振Drive Level 10μW Typ. 100μW. Max.是什么意思? 答:Drive Level属于无源晶振(晶体谐振器)关键参数之一,中文为“激励功率”的意思。 10μW Typ.为典型值; 100μW. Max.为最大值。 若芯片为无源晶振提供的激励功率大于其标称激励功率,就有可能…时间:2025/05/09

晶振Drive Level 10μW Typ. 100μW. Max.是什么意思?

晶振Drive Level 10μW Typ. 100μW. Max.是什么意思? 答:Drive Level属于无源晶振(晶体谐振器)关键参数之一,中文为“激励功率”的意思。 10μW Typ.为典型值; 100μW. Max.为最大值。 若芯片为无源晶振提供的激励功率大于其标称激励功率,就有可能…时间:2025/05/09 -

; ) 无源晶振串联0欧姆电阻串联在哪里?

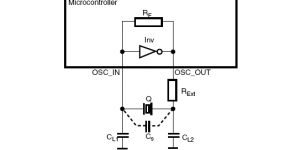

(无源晶振电路中0欧姆串联电阻位置:Rext处) 无源晶振串联0欧姆电阻串联在哪里? 答:0欧姆串联电阻通常位于晶振与微控制器时钟信号输出脚之间。 串联0欧姆电阻具体位置如下: 晶振频率管脚:电阻的一端连接晶振的其中一个频率引脚。 芯片时钟信号输出脚:电阻的另一端连接微控制器的时钟输出引脚(OSC_…时间:2025/04/06

无源晶振串联0欧姆电阻串联在哪里?

(无源晶振电路中0欧姆串联电阻位置:Rext处) 无源晶振串联0欧姆电阻串联在哪里? 答:0欧姆串联电阻通常位于晶振与微控制器时钟信号输出脚之间。 串联0欧姆电阻具体位置如下: 晶振频率管脚:电阻的一端连接晶振的其中一个频率引脚。 芯片时钟信号输出脚:电阻的另一端连接微控制器的时钟输出引脚(OSC_…时间:2025/04/06