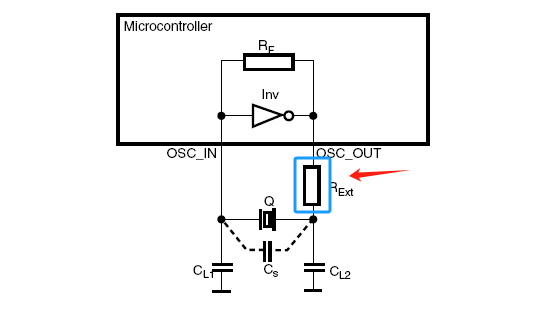

晶振的限流电阻太大会有什么影响?

在数字电路中,为晶振的OSC_OUT引脚串接的限流电阻(Rext或Rd或Rs),通常称为串联电阻或阻尼电阻。如果取值过大,可能会产生一系列负面影响。

这个电阻的主要作用通常是:

![]() 限制驱动电流,防止芯片内部的振荡器电路对晶振产生过驱动。

限制驱动电流,防止芯片内部的振荡器电路对晶振产生过驱动。

![]() 提供阻尼,抑制高次谐波,使振荡更纯净、稳定。

提供阻尼,抑制高次谐波,使振荡更纯净、稳定。

![]() 在极端情况下(如引脚短路)提供一定保护。

在极端情况下(如引脚短路)提供一定保护。

当这个电阻值太大时,会产生以下影响:

1、 最直接和常见的后果:启动困难或无法起振

原理:振荡器电路需要从噪声中获取微弱的信号,经过放大和反馈,建立起稳定的振荡。过大的串联电阻严重衰减了从晶振反馈回输入端的信号能量,使得环路增益不足以克服晶振和电路的损耗。

现象:系统上电后,时钟无法产生;或者在某些条件下(如温度变化、电压波动)随机性地不起振。

2、 振荡幅度不足

即使能够起振,反馈信号的幅度也会因为电阻的衰减而变小。这可能导致时钟信号的高、低电平不完整,下游电路(如MCU、数字芯片)可能无法可靠地识别时钟边沿,导致系统工作不稳定、误动作或通信错误。

3、 频率稳定性变差,易受干扰

振荡环路变得“脆弱”,对外部杂散电容、电源噪声、电磁干扰更敏感。可能导致时钟频率发生微小偏移(频率漂移),或者在噪声影响下产生抖动。

4、 驱动能力下降,影响负载电容匹配

晶振的频率与它的负载电容密切相关。串联电阻过大会改变交流回路中的阻抗特性,影响有效的负载电容值。这可能导致振荡频率偏离标称值(频率精度变差)。

5、 在极端情况下,可能导致间歇性工作

系统在常温下可能正常工作,但在高温(电阻特性变化、芯片驱动能力下降)或低温时停止振荡。