-

; ) 如何驱动晶振?

关于如何驱动晶振,晶诺威科技解释如下: 针对有源晶振,为其提供正常工作时的额定电压值即可,一般可接受电压上下浮动为额定电压的10%。举例,如果额定电压为3.3V,正常供电为:2.97V~3.63V。超出工作电压范围(除非选择晶诺威产宽压系列有源晶振),晶体振荡器的频率稳定度会受到电源电压变动和负载变…时间:2024/09/25

如何驱动晶振?

关于如何驱动晶振,晶诺威科技解释如下: 针对有源晶振,为其提供正常工作时的额定电压值即可,一般可接受电压上下浮动为额定电压的10%。举例,如果额定电压为3.3V,正常供电为:2.97V~3.63V。超出工作电压范围(除非选择晶诺威产宽压系列有源晶振),晶体振荡器的频率稳定度会受到电源电压变动和负载变…时间:2024/09/25 -

; ) 有源晶振需要串联电阻吗?

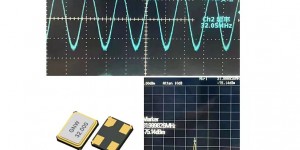

有源晶振需要串联电阻吗? 答:在有源晶振应用电路中,一般不需要串联电阻。 如上图所示: 当发生信号反射或/及信号完整性受损时,可以尝试增加一个低阻值串联电阻,选值一般为几十欧姆,如20~50欧姆。时间:2024/09/05

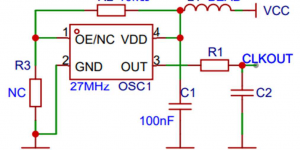

有源晶振需要串联电阻吗?

有源晶振需要串联电阻吗? 答:在有源晶振应用电路中,一般不需要串联电阻。 如上图所示: 当发生信号反射或/及信号完整性受损时,可以尝试增加一个低阻值串联电阻,选值一般为几十欧姆,如20~50欧姆。时间:2024/09/05 -

; ) 关于外接电容COG(NPO)贴片电容选型注意事项

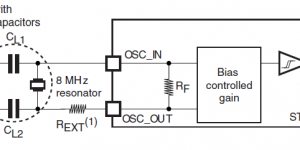

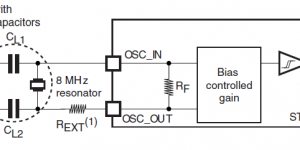

(无源晶振电路中的外接匹配电容CL1和CL2) COG(NPO)贴片电容简述 COG(NPO)贴片电容属于Class 1温度补偿型电容。它的容量稳定,几乎不随温度、电压、时间的变化而变化。尤其适用于高频电子电路。 COG(NPO)贴片电容特性 具有最高的电容量稳定性,在-55℃~125℃工作温度范围…时间:2024/08/18

关于外接电容COG(NPO)贴片电容选型注意事项

(无源晶振电路中的外接匹配电容CL1和CL2) COG(NPO)贴片电容简述 COG(NPO)贴片电容属于Class 1温度补偿型电容。它的容量稳定,几乎不随温度、电压、时间的变化而变化。尤其适用于高频电子电路。 COG(NPO)贴片电容特性 具有最高的电容量稳定性,在-55℃~125℃工作温度范围…时间:2024/08/18 -

; ) 关于晶振电路抗扰性及优化方案

关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…时间:2024/08/17

关于晶振电路抗扰性及优化方案

关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…时间:2024/08/17 -

; ) 两脚晶振引脚可以一脚接地吗?

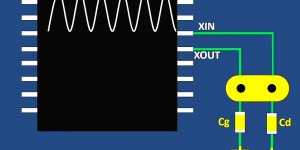

两脚晶振引脚可以一脚接地吗? 答:在皮尔斯振荡电路(绝大多数应用)中,晶振的任一频率管脚均不可以接地,否则将导致晶振停振。 晶诺威科技解释如下: 三脚或四脚晶振具备单独接地脚,建议接地脚接地。但是两脚晶振没有接地脚,只有两个频率管脚(频率输入脚或输出脚),均不可接地。 两脚晶振范例如下: 但是,在密…时间:2024/07/20

两脚晶振引脚可以一脚接地吗?

两脚晶振引脚可以一脚接地吗? 答:在皮尔斯振荡电路(绝大多数应用)中,晶振的任一频率管脚均不可以接地,否则将导致晶振停振。 晶诺威科技解释如下: 三脚或四脚晶振具备单独接地脚,建议接地脚接地。但是两脚晶振没有接地脚,只有两个频率管脚(频率输入脚或输出脚),均不可接地。 两脚晶振范例如下: 但是,在密…时间:2024/07/20 -

; ) 关于晶振周边电路及晶振匹配电路常见问题及分析

关于晶振周边电路及晶振匹配电路常见问题,晶诺威科技分析如下: 如果晶振经过验证被确认为良品,那么确实需要进一步排查晶振周围的电路以及与电路的匹配问题。以下是详细的排查步骤: 1、检查线路连接 使用万用表:使用万用表的“响铃”功能或电阻档来检查晶振与周围电路的连接是否存在虚焊或短路。虚焊点可能表现为高…时间:2024/06/18

关于晶振周边电路及晶振匹配电路常见问题及分析

关于晶振周边电路及晶振匹配电路常见问题,晶诺威科技分析如下: 如果晶振经过验证被确认为良品,那么确实需要进一步排查晶振周围的电路以及与电路的匹配问题。以下是详细的排查步骤: 1、检查线路连接 使用万用表:使用万用表的“响铃”功能或电阻档来检查晶振与周围电路的连接是否存在虚焊或短路。虚焊点可能表现为高…时间:2024/06/18 -

; ) 如何最大程度减少晶振电路中的串扰信号及EMI?

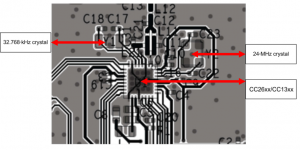

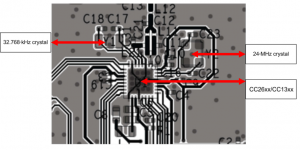

如何最大程度减少晶振电路中的串扰信号及EMI?晶诺威科技解答如下: ( Low-Frequency Oscillator with Quartz Crystal 32.768KHz) As is shown above,The oscillator circuit consists of an in…时间:2024/06/08

如何最大程度减少晶振电路中的串扰信号及EMI?

如何最大程度减少晶振电路中的串扰信号及EMI?晶诺威科技解答如下: ( Low-Frequency Oscillator with Quartz Crystal 32.768KHz) As is shown above,The oscillator circuit consists of an in…时间:2024/06/08 -

; ) 晶振是什么以及晶振的作用

晶振是什么以及晶振的作用 答:晶振是一种常用的电子元器件,用于产生稳定的高精度电信号。晶振的作用就是提供时钟信号给CPU、DSP、FPGA等芯片,确保其系统正常运行。 石英晶体振荡器是信号源的核心所在。在构建各种电子设备及通信系统设备等过程中,石英晶体振荡器周围的电路结构及设计对系统能否最大程度发挥…时间:2024/05/10

晶振是什么以及晶振的作用

晶振是什么以及晶振的作用 答:晶振是一种常用的电子元器件,用于产生稳定的高精度电信号。晶振的作用就是提供时钟信号给CPU、DSP、FPGA等芯片,确保其系统正常运行。 石英晶体振荡器是信号源的核心所在。在构建各种电子设备及通信系统设备等过程中,石英晶体振荡器周围的电路结构及设计对系统能否最大程度发挥…时间:2024/05/10 -

; ) 晶振负载对系统有什么影响?

晶振负载对系统有什么影响? 答:晶振负载的大小会影响晶振的谐振频率和振荡稳定性,如果负载电容过小,会导致晶振频率偏高、振荡稳定性变差;如果负载电容过大,则会导致晶振频率偏低、振荡幅度变小。时间:2024/05/07

晶振负载对系统有什么影响?

晶振负载对系统有什么影响? 答:晶振负载的大小会影响晶振的谐振频率和振荡稳定性,如果负载电容过小,会导致晶振频率偏高、振荡稳定性变差;如果负载电容过大,则会导致晶振频率偏低、振荡幅度变小。时间:2024/05/07 -

; ) 有源晶体振荡器需要额外增加负载电容吗?

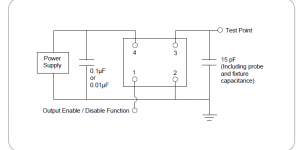

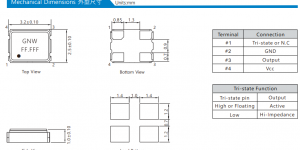

有源晶体振荡器需要额外增加负载电容吗? 答:不需要。 晶诺威科技解释如下: 一般情况下,晶诺威科技生产的有源晶振在实际电路应用中是不需要额外增加任何负载电容的。其具体使用方式为:脚1三态/悬空、脚2接地、脚3输出、脚4电源。 (晶诺威科技产有源晶体振荡器OSC3225引脚/焊盘功能说明) 补充说明:…时间:2024/05/06

有源晶体振荡器需要额外增加负载电容吗?

有源晶体振荡器需要额外增加负载电容吗? 答:不需要。 晶诺威科技解释如下: 一般情况下,晶诺威科技生产的有源晶振在实际电路应用中是不需要额外增加任何负载电容的。其具体使用方式为:脚1三态/悬空、脚2接地、脚3输出、脚4电源。 (晶诺威科技产有源晶体振荡器OSC3225引脚/焊盘功能说明) 补充说明:…时间:2024/05/06