-

; ) 晶振的ESR大了会导致什么问题?

晶振的ESR大了会导致什么问题? 答:晶振的等效串联电阻(ESR)变大,是导致电路故障(尤其是启动失败和稳定性问题)的一个常见但容易被忽略的原因。 ESR变大,对电路是坏事,通常会导致晶振起振困难、停振,或在特定条件下(如低温)失效。 换句话说,ESR增大相当于增大了振荡环路的阻尼,需要电路提供更强…时间:2026/02/26

晶振的ESR大了会导致什么问题?

晶振的ESR大了会导致什么问题? 答:晶振的等效串联电阻(ESR)变大,是导致电路故障(尤其是启动失败和稳定性问题)的一个常见但容易被忽略的原因。 ESR变大,对电路是坏事,通常会导致晶振起振困难、停振,或在特定条件下(如低温)失效。 换句话说,ESR增大相当于增大了振荡环路的阻尼,需要电路提供更强…时间:2026/02/26 -

; ) 晶振的输出频率快了怎么解决?

晶振的输出频率快了怎么解决? 答:首选排查点:负载电容和晶振本体,这是最可能、最容易解决的问题。 1、负载电容 晶振的频率主要由其自身和外部匹配的负载电容共同决定。负载电容变小,频率会向晶振的标称串联谐振频率偏移,导致频率变快。 核对BOM和原理图,确认设计使用的负载电容值(CL1, CL2)是否正…时间:2026/02/25

晶振的输出频率快了怎么解决?

晶振的输出频率快了怎么解决? 答:首选排查点:负载电容和晶振本体,这是最可能、最容易解决的问题。 1、负载电容 晶振的频率主要由其自身和外部匹配的负载电容共同决定。负载电容变小,频率会向晶振的标称串联谐振频率偏移,导致频率变快。 核对BOM和原理图,确认设计使用的负载电容值(CL1, CL2)是否正…时间:2026/02/25 -

; ) 如果晶振坏了CPU处理器还能启动吗?

如果晶振坏了CPU处理器还能启动吗? 答:不能,CPU无法正常启动和工作。 你可以把晶振比作电子系统的心脏或节拍器。它的核心作用是产生一个非常稳定、精确的时钟信号。 时钟信号: 是一连串连续、均匀的方波脉冲,就像指挥家手中的指挥棒或十字路口的红绿灯。 CPU的工作方式: CPU内部由数百万甚至上亿个…时间:2026/02/24

如果晶振坏了CPU处理器还能启动吗?

如果晶振坏了CPU处理器还能启动吗? 答:不能,CPU无法正常启动和工作。 你可以把晶振比作电子系统的心脏或节拍器。它的核心作用是产生一个非常稳定、精确的时钟信号。 时钟信号: 是一连串连续、均匀的方波脉冲,就像指挥家手中的指挥棒或十字路口的红绿灯。 CPU的工作方式: CPU内部由数百万甚至上亿个…时间:2026/02/24 -

; ) 晶振低温不起振的原因是什么?

晶振低温不起振的原因是什么? 答:晶振在低温环境下不起振是一个常见的可靠性问题,主要原因涉及石英晶体谐振器及外围电路的物理特性变化。关于晶振低温不起振的原因,晶诺威科技进一步分析如下: 一、石英晶体本身的温度特性 1、频率-温度曲线 AT切石英晶体的谐振频率随温度变化呈三次函数曲线(通常AT切石英…时间:2026/02/22

晶振低温不起振的原因是什么?

晶振低温不起振的原因是什么? 答:晶振在低温环境下不起振是一个常见的可靠性问题,主要原因涉及石英晶体谐振器及外围电路的物理特性变化。关于晶振低温不起振的原因,晶诺威科技进一步分析如下: 一、石英晶体本身的温度特性 1、频率-温度曲线 AT切石英晶体的谐振频率随温度变化呈三次函数曲线(通常AT切石英…时间:2026/02/22 -

; ) 关于38KHz晶振分频电路的解释说明

关于38KHz晶振分频电路的解释说明 38.000kHz晶振本身是一个频率源。直接将其分频(通常二分频)可以得到19kHz的音频导频信号(如旧式FM立体声广播副载波)。但更常见的设计目标是得到一个标准的时钟频率,比如 32.768kHz 用于RTC,或者8MHz用于单片机等。 最常见应用:红外遥控发…时间:2026/02/20

关于38KHz晶振分频电路的解释说明

关于38KHz晶振分频电路的解释说明 38.000kHz晶振本身是一个频率源。直接将其分频(通常二分频)可以得到19kHz的音频导频信号(如旧式FM立体声广播副载波)。但更常见的设计目标是得到一个标准的时钟频率,比如 32.768kHz 用于RTC,或者8MHz用于单片机等。 最常见应用:红外遥控发…时间:2026/02/20 -

; ) 有源晶振输出幅度怎么调整?

有源晶振输出幅度怎么调整?晶诺威科技解释如下: 有源晶振是完整的振荡器,其输出幅度主要由内部电路设计决定,在出厂时已固定。用户端的调整空间有限,且主要是衰减而非增强。 有源晶振的输出类型是选型时就必须确定的,它直接决定了幅度: CMOS:最常见,输出摆幅接近电源电压(Vcc到GND)。幅度基本由Vc…时间:2026/02/13

有源晶振输出幅度怎么调整?

有源晶振输出幅度怎么调整?晶诺威科技解释如下: 有源晶振是完整的振荡器,其输出幅度主要由内部电路设计决定,在出厂时已固定。用户端的调整空间有限,且主要是衰减而非增强。 有源晶振的输出类型是选型时就必须确定的,它直接决定了幅度: CMOS:最常见,输出摆幅接近电源电压(Vcc到GND)。幅度基本由Vc…时间:2026/02/13 -

; ) 无源晶振输出幅度(Output Level/Swing)的调整方法

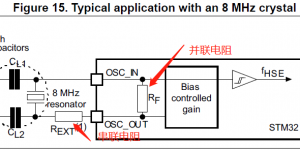

关于无源晶振输出幅度(Output Level/Swing)的调整方法,晶诺威科技解释如下: 无源晶振本身不产生振荡,其幅度由单片机(MCU)内部的振荡器电路和外部匹配网络共同决定。调整的目的是优化增益和功耗,确保可靠起振和稳定运行,而不是随意改变幅度。 核心调整参数:驱动强度(Drive Leve…时间:2026/02/11

无源晶振输出幅度(Output Level/Swing)的调整方法

关于无源晶振输出幅度(Output Level/Swing)的调整方法,晶诺威科技解释如下: 无源晶振本身不产生振荡,其幅度由单片机(MCU)内部的振荡器电路和外部匹配网络共同决定。调整的目的是优化增益和功耗,确保可靠起振和稳定运行,而不是随意改变幅度。 核心调整参数:驱动强度(Drive Leve…时间:2026/02/11 -

; ) 晶诺威科技产有源晶振如何连接芯片?

晶诺威科技产有源晶振如何连接芯片? 连接有源晶振(Crystal Oscillator)相对于无源晶振来说要简单很多,因为其内部已经集成了振荡电路,可以直接输出稳定的时钟信号。 核心思想: 将有源晶振视为一个“时钟信号发生器”,芯片是一个“时钟信号接收者”。一个标准的有源晶振(如四脚贴片封装)通常有…时间:2026/02/10

晶诺威科技产有源晶振如何连接芯片?

晶诺威科技产有源晶振如何连接芯片? 连接有源晶振(Crystal Oscillator)相对于无源晶振来说要简单很多,因为其内部已经集成了振荡电路,可以直接输出稳定的时钟信号。 核心思想: 将有源晶振视为一个“时钟信号发生器”,芯片是一个“时钟信号接收者”。一个标准的有源晶振(如四脚贴片封装)通常有…时间:2026/02/10 -

; ) 系统深度休眠后被RTC唤醒后时间不准是什么原因?

系统深度休眠后被RTC唤醒后时间不准是什么原因? 这是MCU低功耗场景下的常见问题。晶诺威科技分析及总结原因如下: 1、 RTC时钟源问题 LSI(内部低速RC)精度差:通常±2%~5%误差,受温度电压影响; LSE(外部32.768kHz晶振)不稳定:晶振起振慢,负载电容不匹配; 时钟分频配置错误…时间:2026/02/04

系统深度休眠后被RTC唤醒后时间不准是什么原因?

系统深度休眠后被RTC唤醒后时间不准是什么原因? 这是MCU低功耗场景下的常见问题。晶诺威科技分析及总结原因如下: 1、 RTC时钟源问题 LSI(内部低速RC)精度差:通常±2%~5%误差,受温度电压影响; LSE(外部32.768kHz晶振)不稳定:晶振起振慢,负载电容不匹配; 时钟分频配置错误…时间:2026/02/04 -

; ) 电子钟时间不准可以换晶振吗?

电子钟时间不准可以换晶振吗? 答:可以,而且更换晶振通常是修复电子石英钟走时不准的首选和最主要的方法。 为什么换晶振能解决问题? 石英钟的核心计时基准就是那个32.768kHz的无源晶振。这个频率经过芯片内部的分频电路(除以32768),正好得到1Hz的精确秒信号。 1、晶振老化: 随着时间的推移,…时间:2026/02/02

电子钟时间不准可以换晶振吗?

电子钟时间不准可以换晶振吗? 答:可以,而且更换晶振通常是修复电子石英钟走时不准的首选和最主要的方法。 为什么换晶振能解决问题? 石英钟的核心计时基准就是那个32.768kHz的无源晶振。这个频率经过芯片内部的分频电路(除以32768),正好得到1Hz的精确秒信号。 1、晶振老化: 随着时间的推移,…时间:2026/02/02