-

; ) 电子钟换晶振和换外接电容还是慢怎么办?

电子钟换晶振和换外接电容还是慢怎么办? 换了晶振和电容还是走慢,确实让人有点头疼。不过别着急,这通常意味着问题可能出在了我们还没注意到的地方。我们可以用一个简单的“排除法”,一步步把原因找出来。 第一步:从最简单的可能性开始排查 在深入电路内部之前,有几个外部因素很容易被忽略,但影响却很大: 检查电…时间:2026/04/12

电子钟换晶振和换外接电容还是慢怎么办?

电子钟换晶振和换外接电容还是慢怎么办? 换了晶振和电容还是走慢,确实让人有点头疼。不过别着急,这通常意味着问题可能出在了我们还没注意到的地方。我们可以用一个简单的“排除法”,一步步把原因找出来。 第一步:从最简单的可能性开始排查 在深入电路内部之前,有几个外部因素很容易被忽略,但影响却很大: 检查电…时间:2026/04/12 -

; ) 晶振输出波形比较乱是什么原因?

晶振输出波形比较乱是什么原因? 答:晶振输出波形“乱”,通常指的是波形失真、有毛刺、幅度异常或频率不稳。这背后可能涉及电路匹配、PCB布局、外部干扰或器件本身等多个环节。 关于晶振输出波形比较乱问题,晶诺威科技分析如下: 一、核心电路匹配问题 负载电容不匹配: 如果实际电容与晶振规格书要求的负载电容…时间:2026/04/09

晶振输出波形比较乱是什么原因?

晶振输出波形比较乱是什么原因? 答:晶振输出波形“乱”,通常指的是波形失真、有毛刺、幅度异常或频率不稳。这背后可能涉及电路匹配、PCB布局、外部干扰或器件本身等多个环节。 关于晶振输出波形比较乱问题,晶诺威科技分析如下: 一、核心电路匹配问题 负载电容不匹配: 如果实际电容与晶振规格书要求的负载电容…时间:2026/04/09 -

; ) 蓝牙对低频晶振的要求有哪些?

(Bluetooth: Low Energy) 蓝牙对低频晶振的要求有哪些? 这个低频晶振(通常是 32.768kHz)是蓝牙设备在睡眠模式下的“节拍器”,它的精度直接决定了设备的功耗和连接稳定性。建议晶振精度:±10 ppm 到 ±30 ppm。 为什么频率精度如此重要? 晶振频率精度越高,蓝牙设…时间:2026/04/07

蓝牙对低频晶振的要求有哪些?

(Bluetooth: Low Energy) 蓝牙对低频晶振的要求有哪些? 这个低频晶振(通常是 32.768kHz)是蓝牙设备在睡眠模式下的“节拍器”,它的精度直接决定了设备的功耗和连接稳定性。建议晶振精度:±10 ppm 到 ±30 ppm。 为什么频率精度如此重要? 晶振频率精度越高,蓝牙设…时间:2026/04/07 -

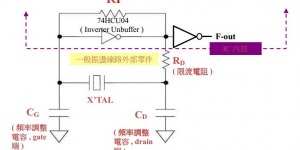

; ) 无源晶振(晶体谐振器)两个外接电容不一样可以吗?

无源晶振(晶体谐振器)两个外接电容不一样可以吗? 答:在绝大多数情况下,不建议将晶振的两个外接电容设计成不一样的,最好使用相同容值的电容。 虽然在某些特定条件下,使用不等值电容是一种调试技巧,但这属于非常规操作,需要谨慎对待。 关于外接电容选择问题,晶诺威科技详解如下: 一、使用相等电…时间:2026/04/05

无源晶振(晶体谐振器)两个外接电容不一样可以吗?

无源晶振(晶体谐振器)两个外接电容不一样可以吗? 答:在绝大多数情况下,不建议将晶振的两个外接电容设计成不一样的,最好使用相同容值的电容。 虽然在某些特定条件下,使用不等值电容是一种调试技巧,但这属于非常规操作,需要谨慎对待。 关于外接电容选择问题,晶诺威科技详解如下: 一、使用相等电…时间:2026/04/05 -

; ) 激励功率过大会导致晶体不起振吗?

激励功率过大会导致晶体不起振吗? 答:是的,激励功率过大的确会导致晶体不起振,甚至造成永久性损坏。 可以把晶体看作一个需要精确能量驱动的"心脏"。激励功率就像是驱动它的"能量": 能量过小(欠激励):心脏跳动无力,无法启动,导致晶体不起振。 能量过大(过激励):这是导致晶体不起振的一个关键原因。过大…时间:2026/04/04

激励功率过大会导致晶体不起振吗?

激励功率过大会导致晶体不起振吗? 答:是的,激励功率过大的确会导致晶体不起振,甚至造成永久性损坏。 可以把晶体看作一个需要精确能量驱动的"心脏"。激励功率就像是驱动它的"能量": 能量过小(欠激励):心脏跳动无力,无法启动,导致晶体不起振。 能量过大(过激励):这是导致晶体不起振的一个关键原因。过大…时间:2026/04/04 -

; ) 无源晶振的负载电容是总电容吗?

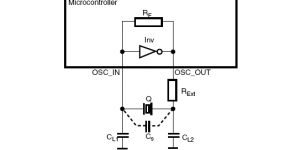

无源晶振的负载电容是总电容吗? 答:是的,可以这么理解。在无源晶振(晶体谐振器)的应用电路中,晶振规格书里标注的“负载电容”就是指从晶振两个引脚看进去的总电容。 它并不是指某一个具体的元件,而是整个外部电路需要满足的一个电气条件或目标值。只有当实际的总电容等于这个值时,晶振才能工作在它所标称的精确频…时间:2026/03/31

无源晶振的负载电容是总电容吗?

无源晶振的负载电容是总电容吗? 答:是的,可以这么理解。在无源晶振(晶体谐振器)的应用电路中,晶振规格书里标注的“负载电容”就是指从晶振两个引脚看进去的总电容。 它并不是指某一个具体的元件,而是整个外部电路需要满足的一个电气条件或目标值。只有当实际的总电容等于这个值时,晶振才能工作在它所标称的精确频…时间:2026/03/31 -

; ) 晶振接地与不接地的区别是什么?

晶振接地与不接地的区别是什么? 答:晶振的接地处理,直接关系到整个系统的电磁兼容性和信号稳定性。 简单来说:如果应用对EMC有要求,晶振的外壳必须接地,而且不是随便接上就行,必须接好。 不接地或接地不良,往往是导致EMC辐射超标和系统不稳定的常见原因之一。 1. 原理:为什么晶振外壳需要接地? 晶振…时间:2026/03/30

晶振接地与不接地的区别是什么?

晶振接地与不接地的区别是什么? 答:晶振的接地处理,直接关系到整个系统的电磁兼容性和信号稳定性。 简单来说:如果应用对EMC有要求,晶振的外壳必须接地,而且不是随便接上就行,必须接好。 不接地或接地不良,往往是导致EMC辐射超标和系统不稳定的常见原因之一。 1. 原理:为什么晶振外壳需要接地? 晶振…时间:2026/03/30 -

; ) 无源晶振频率调节范围是多少?

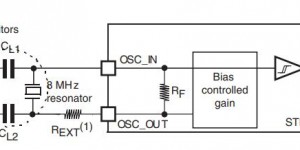

无源晶振频率调节范围是多少? 答:无源晶振的频率调节能力可以概括为:无法大范围调频,但可以小范围精准校准。在实际应用中,±10ppm的调节范围足以补偿因电容误差、电路板寄生参数等因素引起的微小频偏。 关于无源晶振频率调节范围问题,晶诺威科技详解如下: 无源晶振(Crystal Resonator)的…时间:2026/03/25

无源晶振频率调节范围是多少?

无源晶振频率调节范围是多少? 答:无源晶振的频率调节能力可以概括为:无法大范围调频,但可以小范围精准校准。在实际应用中,±10ppm的调节范围足以补偿因电容误差、电路板寄生参数等因素引起的微小频偏。 关于无源晶振频率调节范围问题,晶诺威科技详解如下: 无源晶振(Crystal Resonator)的…时间:2026/03/25 -

; ) 为什么需要抗超声波晶振?

为什么需要抗超声波晶振? 答:常规晶振在超声波封焊工艺中损坏率高。 主要原因如下: 物理损伤:超声波的能量可能会对作为晶振核心材质的石英晶体本身造成损伤,或者破坏其与基座的固着点,导致晶振无法输出频率信号 。 高不良率:常规晶振在过超声波焊接时,不良率通常可能超过30%,这在大规模生产中会显著增加成…时间:2026/03/24

为什么需要抗超声波晶振?

为什么需要抗超声波晶振? 答:常规晶振在超声波封焊工艺中损坏率高。 主要原因如下: 物理损伤:超声波的能量可能会对作为晶振核心材质的石英晶体本身造成损伤,或者破坏其与基座的固着点,导致晶振无法输出频率信号 。 高不良率:常规晶振在过超声波焊接时,不良率通常可能超过30%,这在大规模生产中会显著增加成…时间:2026/03/24 -

; ) 晶振离芯片远了影响大吗?

晶振离芯片远了影响大吗? 答:晶振离芯片较远确实会产生显著影响,高频电路尤为明显。 关于其主要影响,晶诺威科技归纳如下: 1、信号完整性问题 频率越高,影响越大:高频下(如 > 20MHz),时钟信号边沿陡峭,长走线相当于天线,易引发振铃、过冲和反射。 阻抗匹配:走线过长可能导致阻抗不连续,若…时间:2026/03/21

晶振离芯片远了影响大吗?

晶振离芯片远了影响大吗? 答:晶振离芯片较远确实会产生显著影响,高频电路尤为明显。 关于其主要影响,晶诺威科技归纳如下: 1、信号完整性问题 频率越高,影响越大:高频下(如 > 20MHz),时钟信号边沿陡峭,长走线相当于天线,易引发振铃、过冲和反射。 阻抗匹配:走线过长可能导致阻抗不连续,若…时间:2026/03/21