-

; ) 为什么有的晶振一脚接地?

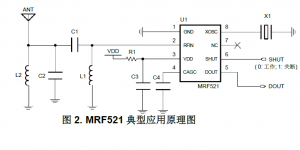

无源晶振一频率引脚接地密勒典型应用电路如下: 比较: 皮尔斯振荡器电路 绝大多数单片机、时钟芯片等使用的晶体振荡电路都是 “皮尔斯振荡器” 的变体。这是一个经典的三点式振荡电路,其核心构成如下: 1、一个反相放大器:位于芯片内部,将信号放大并提供180°的相移。 2、一个晶体:充当高Q值的选频元件,…时间:2025/12/23

为什么有的晶振一脚接地?

无源晶振一频率引脚接地密勒典型应用电路如下: 比较: 皮尔斯振荡器电路 绝大多数单片机、时钟芯片等使用的晶体振荡电路都是 “皮尔斯振荡器” 的变体。这是一个经典的三点式振荡电路,其核心构成如下: 1、一个反相放大器:位于芯片内部,将信号放大并提供180°的相移。 2、一个晶体:充当高Q值的选频元件,…时间:2025/12/23 -

; ) 两脚圆柱晶振一脚接地会怎样?

两脚圆柱晶振一脚接地会怎样? 答:如果将“非接地脚”接地(错误连接),通常情况下可能会导致: 晶振停振:若将本应连接振荡电路的引脚直接接地,会导致振荡回路短路,无法产生振荡信号。 电路失效:MCU或芯片可能无法启动,系统无法正常工作。 两脚晶振的基本原理 1、两脚晶振是无源器件,内部是石英晶体切片,…时间:2025/12/02

两脚圆柱晶振一脚接地会怎样?

两脚圆柱晶振一脚接地会怎样? 答:如果将“非接地脚”接地(错误连接),通常情况下可能会导致: 晶振停振:若将本应连接振荡电路的引脚直接接地,会导致振荡回路短路,无法产生振荡信号。 电路失效:MCU或芯片可能无法启动,系统无法正常工作。 两脚晶振的基本原理 1、两脚晶振是无源器件,内部是石英晶体切片,…时间:2025/12/02 -

; ) nRF52832射频电路参考32MHz+32.768KHz

1、Schematic QFAA and QFAB QFN48 with internal LDO setup 2、 Schematic QFAA and QFAB QFN48 with DC/DC regulator setup 3、 Schematic QFAA and QFAB QFN48 w…时间:2025/12/01

nRF52832射频电路参考32MHz+32.768KHz

1、Schematic QFAA and QFAB QFN48 with internal LDO setup 2、 Schematic QFAA and QFAB QFN48 with DC/DC regulator setup 3、 Schematic QFAA and QFAB QFN48 w…时间:2025/12/01 -

; ) 芯片内部时钟精度、外部时钟晶振精度与外设总线的关系

关于芯片内部时钟、外部时钟晶振与外设总线的关系,晶诺威科技解释如下: 芯片内部时钟(Internal Clock Signal) 芯片内部时钟可能不稳定,一个是不同芯片有误差,同时随着温度的变化,对内部时钟的精度影响很大。芯片内部时钟精度本身也很差,仅为百分之几。 芯片外部时钟(External C…时间:2025/11/29

芯片内部时钟精度、外部时钟晶振精度与外设总线的关系

关于芯片内部时钟、外部时钟晶振与外设总线的关系,晶诺威科技解释如下: 芯片内部时钟(Internal Clock Signal) 芯片内部时钟可能不稳定,一个是不同芯片有误差,同时随着温度的变化,对内部时钟的精度影响很大。芯片内部时钟精度本身也很差,仅为百分之几。 芯片外部时钟(External C…时间:2025/11/29 -

; ) 晶振为什么要校准频偏?

晶振为什么要校准频偏? 晶振校准频偏的本质,是克服其天生的物理缺陷和环境扰动,将其输出频率的准确度和稳定度提升到满足特定应用要求的水平。 换句话说,这是一个在精度、成本和复杂性之间取得平衡的过程。从几毛钱的普通晶振到上千元的高稳晶振(OCXO),其核心区别就在于为了对抗这些频偏因素所采用的技术和工艺…时间:2025/11/23

晶振为什么要校准频偏?

晶振为什么要校准频偏? 晶振校准频偏的本质,是克服其天生的物理缺陷和环境扰动,将其输出频率的准确度和稳定度提升到满足特定应用要求的水平。 换句话说,这是一个在精度、成本和复杂性之间取得平衡的过程。从几毛钱的普通晶振到上千元的高稳晶振(OCXO),其核心区别就在于为了对抗这些频偏因素所采用的技术和工艺…时间:2025/11/23 -

; ) 晶振10uW和100uW有什么区别?

晶振10uW和100uW有什么区别? 首先,这是针对无源晶振(晶体谐振器)的一个关键性电气参数,指的是晶振的激励功率,其单位是uW(即微瓦)。 简单来说,10uW的晶振比100uW的晶振更省电,功耗仅为后者的十分之一。换句话说,10uW的晶振仅需要芯片为其提供10uW的电流就能起振,而100uW的晶…时间:2025/11/22

晶振10uW和100uW有什么区别?

晶振10uW和100uW有什么区别? 首先,这是针对无源晶振(晶体谐振器)的一个关键性电气参数,指的是晶振的激励功率,其单位是uW(即微瓦)。 简单来说,10uW的晶振比100uW的晶振更省电,功耗仅为后者的十分之一。换句话说,10uW的晶振仅需要芯片为其提供10uW的电流就能起振,而100uW的晶…时间:2025/11/22 -

; ) 关于网口晶振25MHz/50MHz辐射超标问题的建议

(晶振辐射超标) 网口EMC辐射超标是硬件设计中非常经典的难题。它的根源往往是一个“干扰源”加上一条“发射天线”的组合——板上的高频噪声(比如晶振的谐波)通过网口这个路径,以共模电流的形式耦合到网线上,而网线本身就是一根高效的 antenna,将噪声辐射出去。 简单来说,网口晶振(如:25MHz/5…时间:2025/11/13

关于网口晶振25MHz/50MHz辐射超标问题的建议

(晶振辐射超标) 网口EMC辐射超标是硬件设计中非常经典的难题。它的根源往往是一个“干扰源”加上一条“发射天线”的组合——板上的高频噪声(比如晶振的谐波)通过网口这个路径,以共模电流的形式耦合到网线上,而网线本身就是一根高效的 antenna,将噪声辐射出去。 简单来说,网口晶振(如:25MHz/5…时间:2025/11/13 -

; ) 若40MHz晶振负载电容为8pF,外部电容选择多大?

若40MHz晶振负载电容为8pF,外部电容选择多大? 答:推荐10pF~12pF。 晶体振荡器的负载电容 CL 由以下公式定义: CL = (C1 × C2) / (C1 + C2) + Cstray 其中: C1, C2:就是我们选择的外部两个电容,通常为了对称,取相同值。 Cstray:是电路的…时间:2025/11/12

若40MHz晶振负载电容为8pF,外部电容选择多大?

若40MHz晶振负载电容为8pF,外部电容选择多大? 答:推荐10pF~12pF。 晶体振荡器的负载电容 CL 由以下公式定义: CL = (C1 × C2) / (C1 + C2) + Cstray 其中: C1, C2:就是我们选择的外部两个电容,通常为了对称,取相同值。 Cstray:是电路的…时间:2025/11/12 -

; ) 32MHz晶振8pF和9pF的区别是什么?

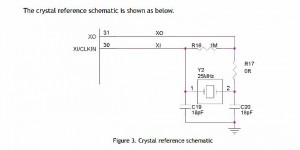

32MHz晶振(32MHz Resonator)8pF和9pF的区别是什么?晶诺威科技解释如下: 32MHz晶振的8pF和9pF指的是其“负载电容”。简单来说,这个区别的核心在于:为了让晶振精确地在32MHz频率上工作,你需要为它匹配不同的外部电容。 1、负载电容是什么? 对于常用的并联谐振型晶振,…时间:2025/11/11

32MHz晶振8pF和9pF的区别是什么?

32MHz晶振(32MHz Resonator)8pF和9pF的区别是什么?晶诺威科技解释如下: 32MHz晶振的8pF和9pF指的是其“负载电容”。简单来说,这个区别的核心在于:为了让晶振精确地在32MHz频率上工作,你需要为它匹配不同的外部电容。 1、负载电容是什么? 对于常用的并联谐振型晶振,…时间:2025/11/11 -

; ) 25MHz晶振两端电压为0是什么原因?

25MHz晶振两端电压为0是什么原因? 25MHz晶振两端电压为0,这是一个典型的电路故障现象。这通常意味着晶振没有起振。 下面我将从原因排查和解决步骤两个方面为您详细解答。 晶振需要和芯片内部的振荡器电路(通常是一个反相放大器)配合,与外部电容一起构成一个皮尔斯振荡器,才能产生稳定的时钟信号。当这…时间:2025/11/10

25MHz晶振两端电压为0是什么原因?

25MHz晶振两端电压为0是什么原因? 25MHz晶振两端电压为0,这是一个典型的电路故障现象。这通常意味着晶振没有起振。 下面我将从原因排查和解决步骤两个方面为您详细解答。 晶振需要和芯片内部的振荡器电路(通常是一个反相放大器)配合,与外部电容一起构成一个皮尔斯振荡器,才能产生稳定的时钟信号。当这…时间:2025/11/10